# Implementation of Distributed Orthogonal Persistence Using Virtual Memory

Francis Vaughan

# Thesis submitted for the degree of Doctor of Philosophy

# in

The University of Adelaide (Faculty of Mathematical and Computer Sciences)

December 1994

Awarded 1995

This work contains no material which has been accepted for the award of any other degree or diploma in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text.

I give consent to this copy of my thesis, when deposited in the University Library, being available for loan and photocopying.

17th August 1995

**SIGNED:**

DATE:

# Abstract

Persistent object systems greatly simplify programming tasks, since they hide the traditional distinction between short-term and long-term storage from the applications programmer. As a result, the programmer can operate at a level of abstraction in which short-term and long-term data are treated uniformly. In the past most persistent systems have been constructed above conventional operating systems and have not supported any form of distributed programming paradigm. In this thesis we explore the implementation of orthogonally persistent systems that make direct use of the attributes of paged virtual memory found in the majority of conventional computing platforms. These attributes are exploited to support object movement for persistent storage to addressable memory, to aid in garbage collection, to provide the illusion of larger storage spaces than the underlying architecture allows, and to provide distribution of the persistent system.

The thesis further explores the different models of distribution, notably a one world model in which a single persistent space exists, and a federated one in which many cooperating spaces exist. It explores communication mechanisms between federated spaces and the problems of maintaining consistency between separate persistent spaces in a manner which ensures both a reliable and resilient computational environment. In particular characterising the interdependencies using vector clocks and the manner in which vector time can be used to provide a complete mechanism for ensuring reliable and resilient computation.

The thesis concludes with a description of a new operating system design in which support for the mechanisms described earlier are intrinsic in the design. This operating system is able to provide orthogonal persistence in a distributed environment with no effort on the part of users of the operating system.

# Acknowledgments

This thesis owes much to many people.

First and foremost thanks go to my parents for their love, support and forbearance over the last few years.

Thanks are due to my supervisor Al Dearle, to whom much is owed, especially for his friendship and encouragement in this endeavour.

Ron Morrison and the persistence group at the University of St Andrews: Richard Conner, Quintin Cutts, Graham Kirby and Dave Munro for advice, encouragement and a never wavering welcome when I landed upon their doorstep.

John Rosenberg and the Grasshopper group at Sydney University: Franz Henskens, Anders Lindström, Rex di Bona, Matty Farrow and Stephen Norris, for their part in the Grasshopper project. Also for the stimulating and rowdy discussions which made the Grasshopper project such a joy to be a part of.

Alex Farkas and David Hulse for their respective contributions to Casper and Grasshopper.

The original members of the Casper group, Tracy Lo Basso, Ruth Fazakerley and Bett Koch for putting up with me.

Chris Barter for support and friendship over many years, without which this would not have been possible.

The members the department at Adelaide University, for providing a convivial home from home for so many years.

# Contents

| Cha  | apter 1. Introduction. |                                 |    |

|------|------------------------|---------------------------------|----|

| 1.1. |                        | Persistence                     | 1  |

| 1.2. |                        | Accidents of History            | 4  |

|      |                        |                                 | 5  |

|      | 1.3.1.                 | Specially designated objects    | 5  |

|      |                        | Embedded persistence            | 7  |

| 8    | 1.3.3.                 | Reachability                    | 7  |

| 1.4. |                        | Distribution                    | 8  |

|      | 1.4.1                  | Single Unstructured             | 8  |

|      | 1.4.2.                 | Structured single address space | 9  |

|      | 1.4.3.                 | Fully partitioned               | 9  |

|      |                        | Federated                       | 10 |

|      | 1.4.4.                 | Difficulties                    | 10 |

| 1.5. |                        | Implementation Mechanisms       | 11 |

|      | 1.5.1                  | Specialised Hardware            | 11 |

|      | 1.5.2                  | Software                        | 11 |

|      |                        | Conventional Hardware           | 12 |

|      | 1.5.3.1                | Granularity                     | 12 |

|      | 1.5.3.2                | Native code support             | 13 |

| 1.6. |                        |                                 | 13 |

|      |                        | Contributions.                  | 14 |

# **Chapter 2. Implementation Tactics.**

| 2.1Introduction                               | 17 |

|-----------------------------------------------|----|

| 2.2Issues                                     | 17 |

| 2.2.1Data Movement                            | 18 |

| 2.2.1.1                                       | 18 |

| 2.2.1.2                                       | 19 |

| 2.2.2. Address Generation                     | 19 |

| 2.2.3Pointer Representation.                  | 20 |

| 2.2.4Garbage Collection                       | 20 |

| 2.2.4.1                                       | 21 |

| 2.2.4.2GC in Persistent Systems               | 22 |

| 2.2.5Basic architectures.                     | 22 |

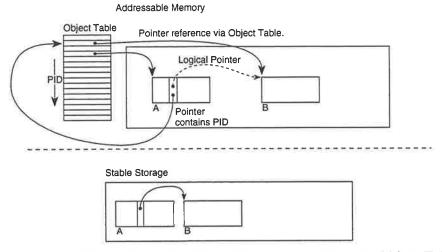

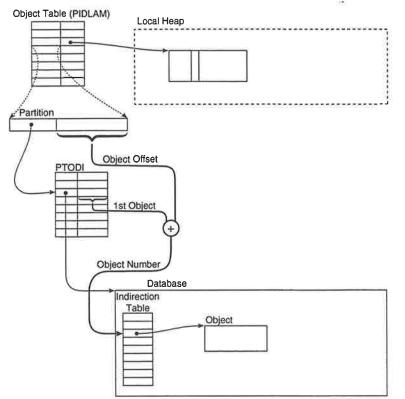

| 2.2.5.1 Object Tables                         | 23 |

| 2.3Hardware                                   | 24 |

| 2.3.1                                         | 25 |

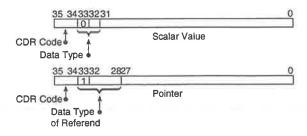

| 2.3.2Lisp Machines                            | 26 |

| 2.3.2.1                                       | 26 |

| 2.3.2.2. Address Generation and Data Movement | 27 |

| 2.3.2.3                                       | 27 |

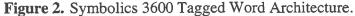

| 2.3.3ORSLA                                    | 28 |

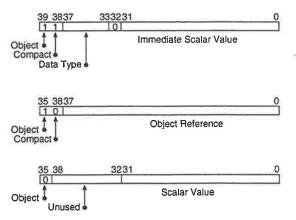

| 2.3.3.1 Data Formats                          | 28 |

| 2.3.3.2Garbage Collection                     | 29 |

| 2.3.3.3Data Movement                          | 30 |

| 2.3.4Rekursiv                                 | 30 |

| 2.3.4.1. Data Movement                        | 31 |

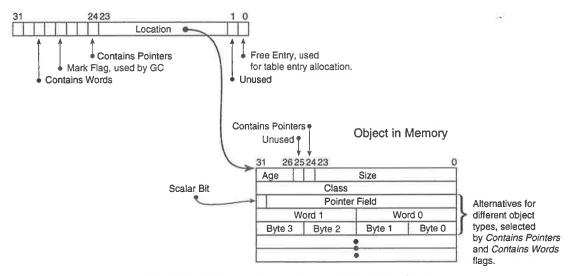

| 2.3.4.2 Object Format                         | 32 |

| 2.3.4.3                                       | 33 |

| 2.4Software                                   | 33 |

| 2.4.1                                         | 34 |

| 2.4.1.1 Recognising Pointers                  | 35 |

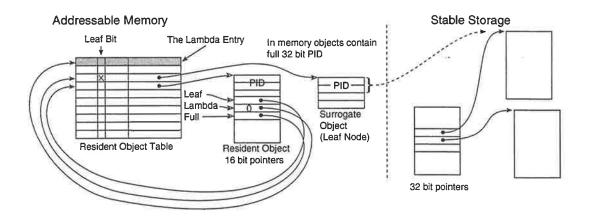

| 2.4.2LOOM                                     | 36 |

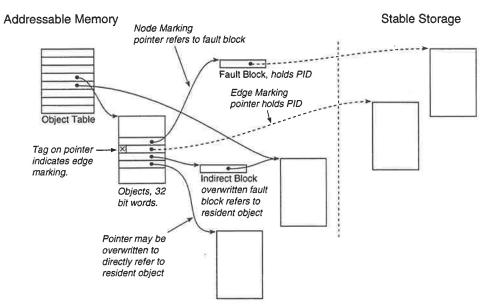

| 2.4.2.1                                       | 38 |

| 2.4.2.2Garbage Collection                     | 41 |

| 2.4.3PS-algol and CPOMS                       | 42 |

| 2.4.3.1                                       | 42 |

| 2.4.3.2Ad                     | dresses in PS-algol and CPOMS    | 42       |

|-------------------------------|----------------------------------|----------|

| 2.4.3.3Dat                    |                                  | 43       |

| 2.4.3.4Ob                     |                                  | 44       |

| 2.4.3.5                       | rbage Collection                 | 45       |

| 2.4.4Na                       | pier-88 and the PAM              | 45       |

| 2.4.4.1PA                     | M                                | 46       |

| 2.4.5Th                       | e POMS Store.                    | 47       |

| 2.4.6Ob                       |                                  | 47       |

| 2.4.6.1                       |                                  | 48       |

| 2.4.6.2                       | dress Generation                 | 49       |

| 2.4.6.3                       | rhage Collection                 | 49       |

| 2.4.0.5. Pac                  |                                  | 50       |

| 2.5. Pag<br>2.5.1. Da         | ta Movement                      | 51       |

| 2.5.1.1                       | e Manning                        | 52       |

| 2.5.2Te                       |                                  | 52       |

| 2.5.2.1                       |                                  | 53       |

| 2.5.2.1                       |                                  | 53       |

| 2.5.2.1.1                     | what Collection                  | 54       |

|                               |                                  | 54       |

| 2.5.2.2                       |                                  | 54       |

|                               |                                  | 55       |

| 2.5.2.2.2Poi                  |                                  | 55       |

| 2.5.2.2.3Ad                   |                                  | 55       |

| 2.6                           |                                  | 55       |

| 2.6.1Int                      | egrated Store Management         | 55<br>55 |

| 2.6.2Da                       |                                  | 55<br>56 |

| 2.6.3Ob                       |                                  | 50<br>59 |

| 2.6.4Ad                       |                                  | 59<br>59 |

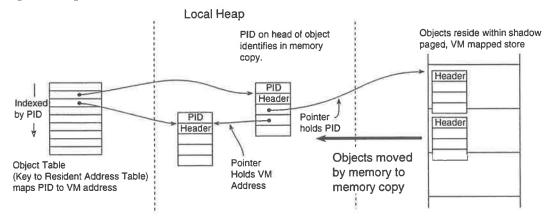

| 2.6.5Lo                       | cal Heaps and Pointer Quarantine | 59<br>59 |

| 2.6.5.1Dis                    |                                  |          |

| 2.6.5.2Co                     | bpy Out Implementation           | 60       |

| 2.6.5.3Ea                     |                                  | 60<br>61 |

| 2.6.5.4La                     | zy Copy-Out                      |          |

| 2.6.5.5Pa                     | ge/Card Based                    | 62       |

| 2.6.6,Sto                     |                                  | 62       |

| 2.6.6.1Op                     | portunistic memory recovery      | 63       |

| 2.6.6.2Fu                     | Ill Garbage Collection           | 63       |

| 2.6.6.2.1Ma                   |                                  | 64       |

| 2.6.6.2.2Tra                  |                                  | 64       |

| 2.6.6.2.3Co                   | ompaction                        | 64       |

| 2.6.6.3Su                     |                                  | 65       |

| 2.7Pe                         | rformance                        | 65       |

| 2.7.1Co                       |                                  | 66       |

| 2.7.1.1Ex                     |                                  | 66       |

| 2.7.1.2Ex                     |                                  | 67       |

| 2.7.1.3Ex                     | ceptions on conventional         |          |

| RI                            | SC architectures                 | 67       |

| 2.7.1.4Ex                     |                                  | 68       |

| 2.7.1.5Ex                     | cceptions in OSF and Mach.       | 68       |

| 2.7.1.6Mo                     | easuring Exception Cost          | 68       |

| 2.7.1.7Bu                     | ailding Exceptions for Speed     | 69       |

| 2.7.2Pa                       | age Granularity                  | 70       |

| 2.7.2.1Pa                     | ge cards vs. remembered sets:    | 70       |

| 2.7.2.2Ot                     | bject Residency Test             | 71       |

| 2.8Co                         | omparisons.                      | 72       |

| 2.8.1No                       | otes.                            | 75       |

|                               |                                  |          |

| Chapter 3. Pointer Swizzling. |                                  |          |

|                               |                                  | 77       |

۲.

17

| 3.4 |                             | A hybrid approach                         | 82   |

|-----|-----------------------------|-------------------------------------------|------|

|     | 3.4.1.                      | Exceptions                                | 84   |

|     | 3.4.2.                      | Data Load.                                | 85   |

|     | 3.4.3.                      |                                           | 86   |

|     | 3.4.4.                      | Deswizzling                               | 88   |

|     | 3.4.4.1.                    | .Deswizzling in Wilson's Scheme           | 90   |

|     | 3.4.4.2.                    | .Deswizzling in the Hybrid Scheme         | 90 · |

|     | 3.4.5.                      | Elaboration of detail                     | 91   |

|     | 3.4.5.1.                    |                                           | 91   |

|     | 3.4.5.2.                    | Pointer comparisons                       | 96   |

|     | 3.4.5.3                     | Large Objects                             | 97   |

|     | 3.4.5.4.                    | Management of the translation table       | 97   |

|     | 3.4.5.5                     | Creation of new objects                   | 97   |

| 3.5 |                             | Comparison of the schemes                 | 98   |

| 3.6 |                             | Conclusions                               | 100  |

|     |                             |                                           |      |

|     | oter 4. Store Architecures. |                                           |      |

|     |                             |                                           | 101  |

| 4.2 |                             |                                           | 101  |

|     | 4.2.1.                      |                                           | 102  |

|     | 4.2.2.                      | .Speed.                                   | 102  |

|     | 4.2.3                       | .Reliability.                             | 102  |

| 4.3 |                             | Stability and Resilience                  | 102  |

|     | 4.3.1                       | .Soft Failure                             | 103  |

|     | 4.3.2                       | .Hard failure                             | 103  |

|     | 4.3.3                       | .Site Failure                             | 105  |

| 4.4 |                             | .System reference model                   | 105  |

|     | 4.4.1.                      | .Self Consistency                         | 107  |

|     | 4.4.2.                      | Synchronous and Asynchronous Creation of  |      |

|     |                             | Persistent State.                         | 107  |

| . – | 4.4.3.                      |                                           | 108  |

| 4.5 |                             | Mechanisms                                | 109  |

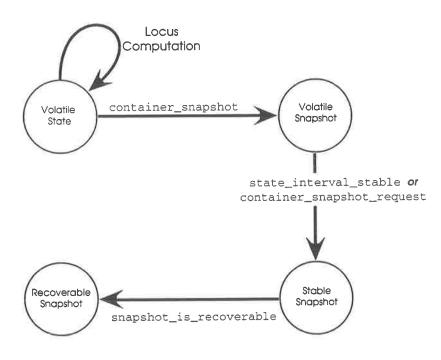

|     | 4.5.1.                      | Snapshots                                 | 109  |

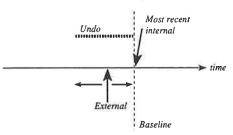

|     | 4.5.2.                      | Incremental baseline generation           | 109  |

|     | 4.5.3.                      | Logging.                                  | 110  |

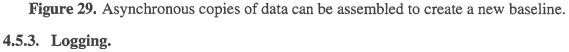

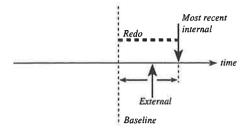

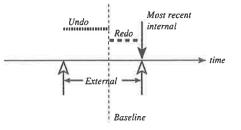

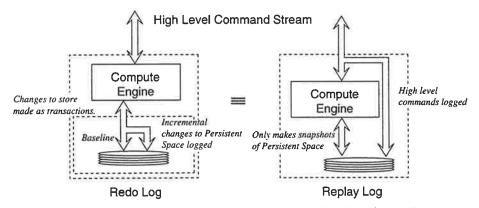

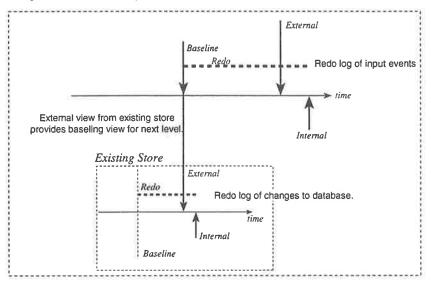

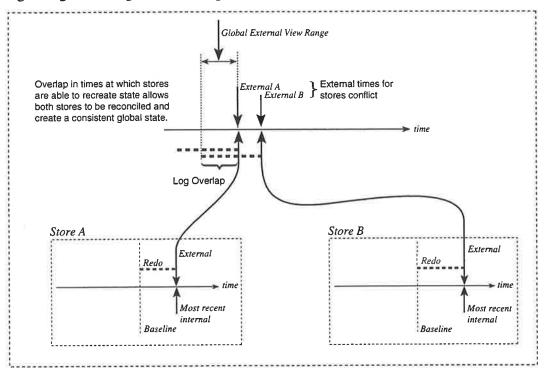

|     | 4.5.3.1.                    | .Modelling Logging.                       | 110  |

|     |                             | .Undo and Redo in the one store.          | 112  |

|     | 4.5.3.3.                    | Recovering logs                           | 112  |

|     | 4.5.3.4.                    | Replay Logging                            | 113  |

|     | 4.5.4.                      | Nested Store Strategies                   | 114  |

| 10  | 4.5.5                       | Output in replay systems                  | 114  |

|     |                             | Concurent Access, Distributed Systems and |      |

|     | 4 6 1                       | . Multiple stores.                        | 115  |

|     | 4.6.1.                      | Causality Tracking                        | 116  |

|     | 4.6.2.                      | Replay of Output.                         | 116  |

| 47  | 4.6.3                       |                                           | 117  |

|     |                             |                                           | 118  |

| 4.8 | 4 0 1                       | . Implementation Strategies.              | 118  |

|     | 4.8.1.                      |                                           | 119  |

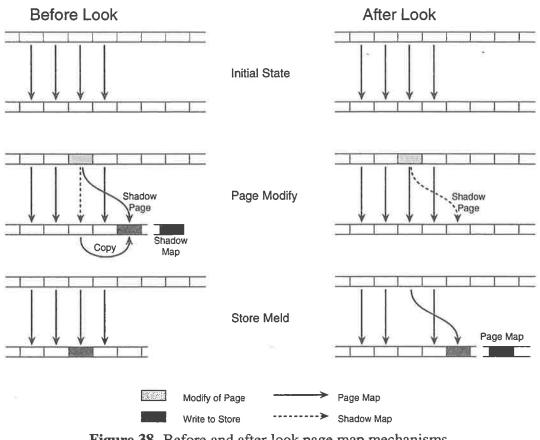

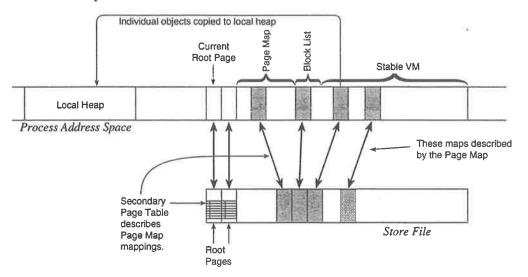

|     | 4.8.2.                      | After Look                                | 120  |

|     | 4.8.2.1.                    |                                           | 120  |

|     | 4.8.2.2.                    |                                           | 121  |

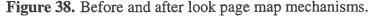

|     | 4.8.2.3.                    | . Shauow Paging                           | 121  |

|     | 4.8.2.5.                    | Object Shadowing                          | 122  |

| 10  | 4.8.3                       | Conclusions                               | 123  |

| 4.7 |                             | Conclusions                               | 123  |

. 01. 20

| Chapter 5. Implemetation Strategies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 125 |

| 5.2Related Work.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 125 |

| 5.2.1Shrines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 125 |

| 5.2.2Page Based Napier88 Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125 |

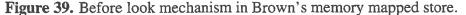

| 5.2.3Browns Before-Look Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 125 |

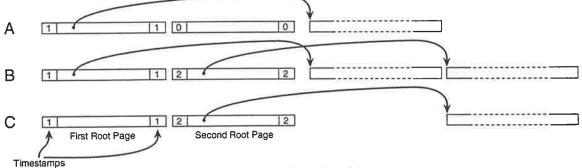

| 5.2.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 126 |

| 5.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120 |

| 5.2.4. Thete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 127 |

| 5.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 5.2.6. Logging Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 131 |

| 5.2.7RVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 131 |

| 5.2.8Texas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 132 |

| 5.2.9Mneme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 133 |

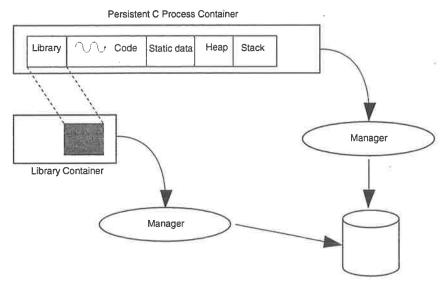

| 5.3CASPER Bi-Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 135 |

| 5.3.1Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 135 |

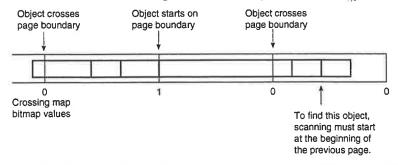

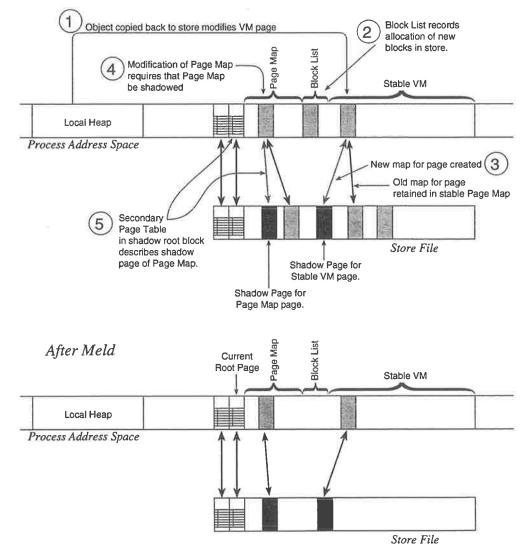

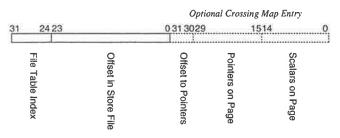

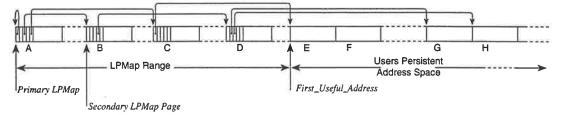

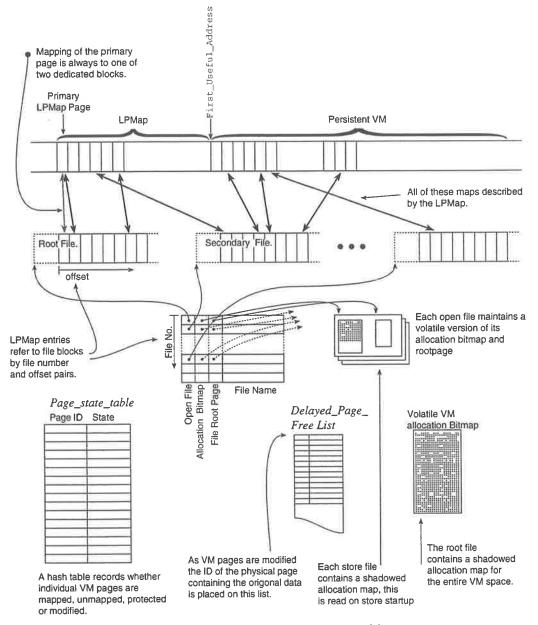

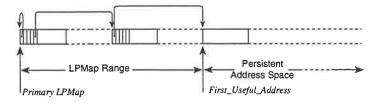

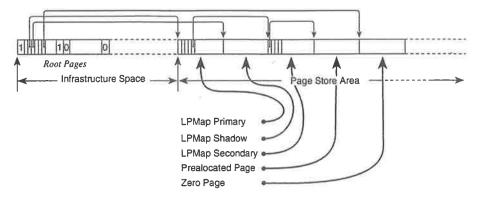

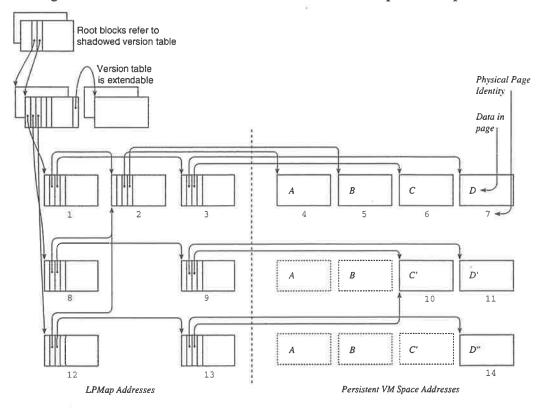

| 5.3.2Page Map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 136 |

| 5.3.3Store Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 137 |

| 5.3.4Store Creation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 139 |

| 5.3.5Secondary Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 140 |

| 5.3.6Store Start-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 140 |

| 5.3.7Napier88 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 141 |

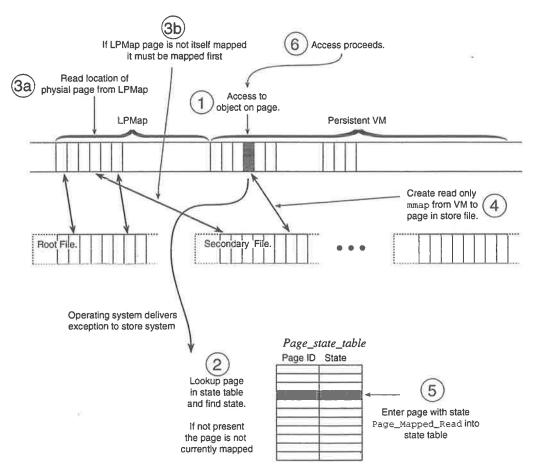

| 5.3.8Runtime Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 142 |

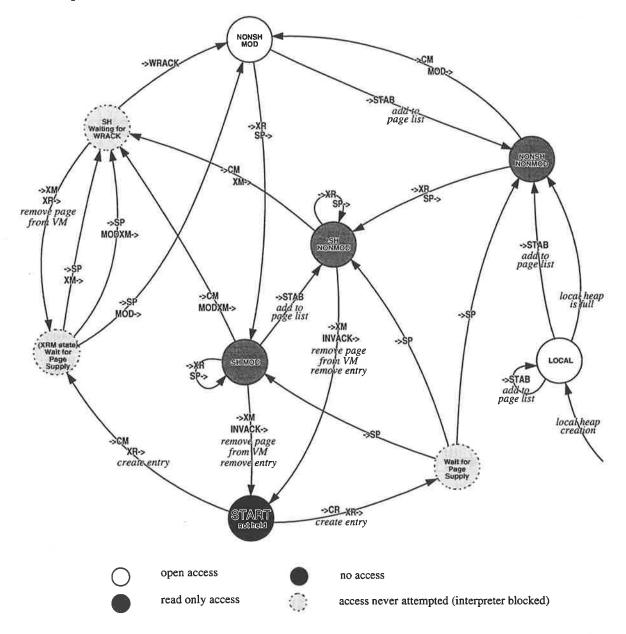

| 5.3.8.1Page States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 142 |

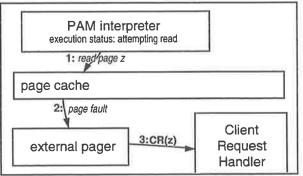

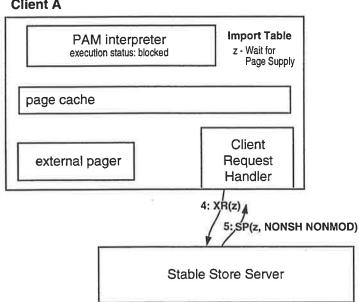

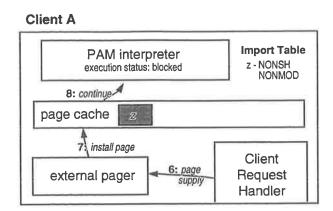

| 5.3.8.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 142 |

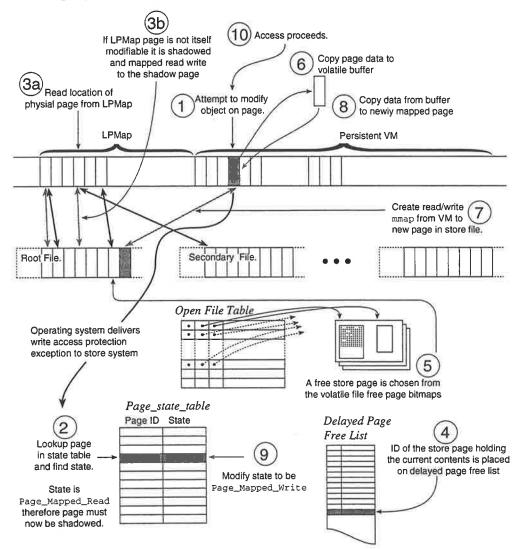

| 5.3.8.3Write Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 144 |

| 5.3.8.4LPMap mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 145 |

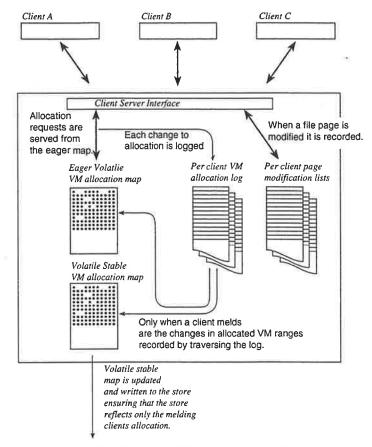

| 5.3.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 146 |