# Fast Asynchronous VLSI Circuit Design Techniques and their Application to Microprocessor Design

Shannon V. Morton, B. E. (Hons.)

Department of Electrical and Electronic Engineering The University of Adelaide Adelaide, South Australia.

January 22, 1997

## Addenda

#### Section 2.2 - Asynchronous hardware

This thesis is focussed on practical asynchronous circuit design with an emphasis on microprocessors, and therefore only those processors which have been designed to fabrication have been included in the literature discussion. Fabricated test structures and coded microprocessors do not provide enough reliable data to justify their discussion in this context, although in Section 8.1 a description of coded superscalar processors, as compared to the author's, is given.

#### Section 2.2.2 - AMULET I and II

The AMULET I design was the first generation attempt at implementing a sixth generation commercial ARM6 processor, and was built with significantly less man-power and resources. This makes comparisons between them difficult, and the performance gap of 50% should be treated cautiously. The subsequent AMULET II processor has since demonstrated improved performance over the ARM6.

#### Section 3.5 - The ECS representation

The ECS representation is intended to enable asynchronous circuits to be specified in a clear and concise format which models the interaction of data and control wires. It is not intended as a formal tool for synthesis, and as such has not been developed using formal methods. Instead, an intuitive description of the representation has been presented based on the practical implementation of asynchronous circuits, as this is the major focus of the thesis.

#### Section 4.1 - Algebraic improvements of a TS

The simplifications described in this section are synonymous with those of boolean logic.

#### Section 5.3.1 - Dynamic logic

The nature of the data stream will also impact the power dissipation of a dynamic versus a static gate.

#### Section 5.3.3.2 - Self-timed pseudo-nmos logic

This circuit has a fast completion detection time compared to the static logic tree, as evidenced in Table 6.8. Compared to a typical dynamic gate however, it will be slow.

#### **Chapter 6 - Self-timed Architectures**

The pseudo self-timed architectures presented in this chapter do not require additional safety margins. The computation and completion paths are closely matched in layout, and an implicit margin is already included in the handshaking overhead to compensate for any variations.

### Errata

Page 47, line 1: "sinks input" should read "sink's input"

Page 77, line 2: "though" should read "through"

Page 86, line 3: "is" should read "are"

Page 99, line 29: "need" should read "needed"

Page 123, line 11: "best the there" should read "best there"

Page 155, line 11: "blocks" should read "block"

# Contents

| Abstra  | act      |                                    | ix  |

|---------|----------|------------------------------------|-----|

| Declar  | ation    |                                    | x   |

| Prefac  | e        |                                    | xi  |

| Ackno   | wledge   | ments                              | xii |

| List of | f Figure | es x                               | iii |

| List of | f Tables | з х                                | vi  |

| 1 Int   | roducti  | on                                 | 1   |

| 1.1     | Advan    | tages of asynchronous systems      | 2   |

|         | 1.1.1    | Global communication               | 2   |

|         | 1.1.2    | Data dependent computation times   | 3   |

|         | 1.1.3    | Resilience to operating conditions | 3   |

|         | 1.1.4    | Reduced power dissipation          | 4   |

|         | 1.1.5    | Incremental improvements           | 4   |

|         | 1.1.6    | Synthesis and verification         | 4   |

|         | 1.1.7    | Power spectrum                     | 5   |

| 1.2     | Disad    | vantages of asynchronous systems   | 5   |

|         | 1.2.1    | Control complexity                 | 5   |

|         | 1.2.2    | Testability                        | 5   |

|         | 1.2.3    | Area overhead                      | 6   |

|         | 1.2.4    | Operating speed                    | 6   |

|         | 1.2.5    | Integration and software support   | 7   |

|   | 1.3 | Asynch  | nronous paradigms                            | 7         |

|---|-----|---------|----------------------------------------------|-----------|

|   |     | 1.3.1   | Timing assumptions                           | 7         |

|   |     | 1.3.2   | Control signalling                           | 8         |

|   |     | 1.3.3   | Signal encoding                              | 9         |

|   |     | 1.3.4   | Summary                                      | 10        |

|   | 1.4 | Thesis  | outline                                      | 10        |

| • | ות  |         | 7 1 -                                        | 12        |

| 2 |     | ated W  |                                              | 12        |

|   | 2.1 | v       | esis and verification                        | 12        |

|   |     | 2.1.1   | Tangram                                      |           |

|   |     | 2.1.2   | Communicating processes                      |           |

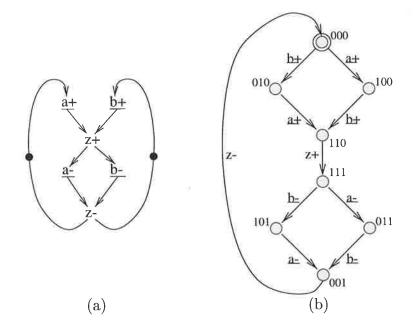

|   |     | 2.1.3   | Signal transition graphs (STGs)              |           |

|   |     | 2.1.4   | STG related synthesis                        |           |

|   |     | 2.1.5   | Other contributions                          |           |

|   | 2.2 | Asyncl  | hronous hardware                             | 15        |

|   |     | 2.2.1   | Micropipelines and the CFPP                  | 16        |

|   |     | 2.2.2   | AMULET I and II                              | 17        |

|   |     | 2.2.3   | DCC error detector                           | 17        |

|   |     | 2.2.4   | Caltech microprocessor                       | 18        |

|   |     | 2.2.5   | Other contributions                          | 18        |

|   | 2.3 | Summ    | ary of related works                         | 18        |

|   | 2.4 | A need  | d for speed                                  | 19        |

| 3 | Eve | ent Cor | ntrolled Systems (ECS) Design Representation | <b>21</b> |

| - | 3.1 |         | ntions                                       | 21        |

|   | 3.2 |         | controlled elements                          |           |

|   | 0.1 | 3.2.1   | Muller-C element                             |           |

|   |     | 3.2.2   | Merge gate                                   |           |

|   |     | 3.2.3   | Send gate                                    |           |

|   |     | 3.2.4   | Feed gate                                    |           |

|   |     | 3.2.5   | Restore gate                                 |           |

|   |     | 3.2.6   | Until gate                                   |           |

|   |     | 3.2.7   | Latching element                             |           |

|   |     | ··•••   |                                              |           |

|   |      | 3.2.8                                                                                                                                              | Delays and logic functions                         | 29                                                                    |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------|

|   |      | 3.2.9                                                                                                                                              | Relative gate speeds                               | 29                                                                    |

|   |      | 3.2.10                                                                                                                                             | Micropipeline module exceptions                    | 29                                                                    |

|   | 3.3  | Some                                                                                                                                               | formalisms for gate representations                | 30                                                                    |

|   | 3.4  | Analys                                                                                                                                             | sis of methodologies                               | 31                                                                    |

|   | 3.5  | The E                                                                                                                                              | CS representation                                  | 33                                                                    |

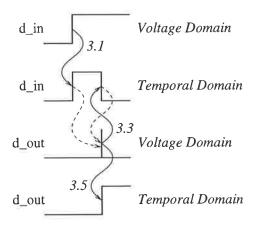

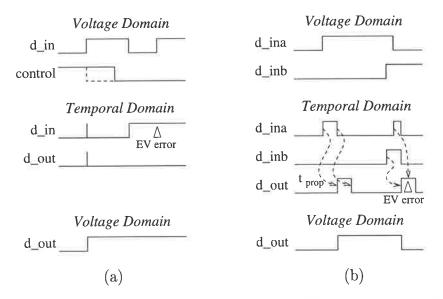

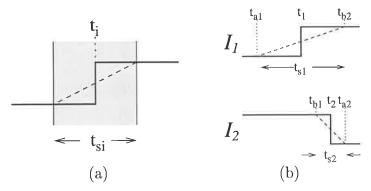

|   |      | 3.5.1                                                                                                                                              | Transforming signals into the temporal domain      | 34                                                                    |

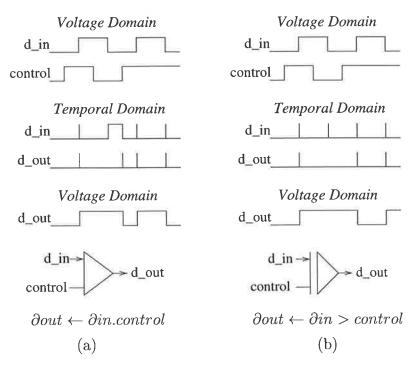

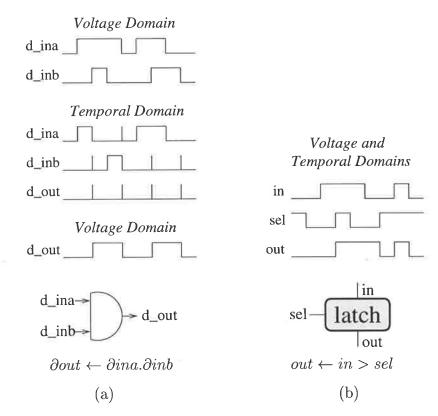

|   |      | 3.5.2                                                                                                                                              | ECS operators and temporal equations               | 36                                                                    |

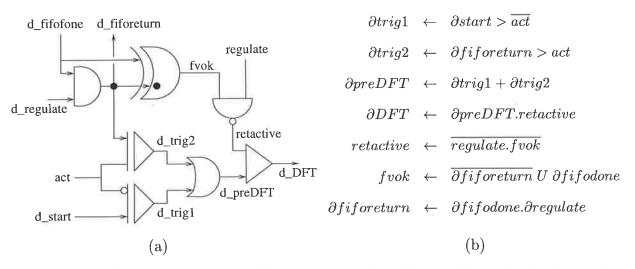

|   |      | 3.5.3                                                                                                                                              | Some ECS gate examples                             | 40                                                                    |

|   |      | 3.5.4                                                                                                                                              | Comparative gate representations                   | 43                                                                    |

|   |      | 3.5.5                                                                                                                                              | Some example TS's and their corresponding circuits | 43                                                                    |

|   |      | 3.5.6                                                                                                                                              | Precedence and properties of temporal operators    | 45                                                                    |

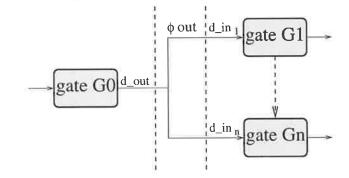

|   |      | 3.5.7                                                                                                                                              | Interconnectivity of gates in ECS                  | 46                                                                    |

|   |      | 3.5.8                                                                                                                                              | Principles of error detection                      | 47                                                                    |

|   | 3.6  | Summ                                                                                                                                               | nary                                               | 50                                                                    |

| 4 | Fast | t Asvn                                                                                                                                             | chronous Circuit Techniques                        | 51                                                                    |

| т |      | -                                                                                                                                                  |                                                    |                                                                       |

|   | 11   | Algeh                                                                                                                                              | raic improvements of a $TS$                        | 51                                                                    |

|   | 4.1  |                                                                                                                                                    | raic improvements of a TS                          |                                                                       |

|   | 4.1  | 4.1.1                                                                                                                                              | Useless TE substitutions                           | 54,                                                                   |

|   | 4.1  | 4.1.1<br>4.1.2                                                                                                                                     | Useless TE substitutions                           | 54.<br>55                                                             |

|   |      | 4.1.1<br>4.1.2<br>4.1.3                                                                                                                            | Useless TE substitutions                           | 54、<br>55<br>55                                                       |

|   | 4.1  | 4.1.1<br>4.1.2<br>4.1.3<br>Impro                                                                                                                   | Useless TE substitutions                           | 54、<br>55<br>55                                                       |

|   |      | 4.1.1<br>4.1.2<br>4.1.3<br>Impro<br>4.2.1                                                                                                          | Useless TE substitutions                           | 54,<br>55<br>55<br>56                                                 |

|   |      | 4.1.1<br>4.1.2<br>4.1.3<br>Impro<br>4.2.1<br>4.2.2                                                                                                 | Useless TE substitutions                           | 54,<br>55<br>55<br>56<br>59                                           |

|   | 4.2  | 4.1.1<br>4.1.2<br>4.1.3<br>Impro<br>4.2.1<br>4.2.2<br>4.2.3                                                                                        | Useless TE substitutions                           | 54,<br>55<br>55<br>56<br>59<br>60                                     |

|   |      | 4.1.1<br>4.1.2<br>4.1.3<br>Impro<br>4.2.1<br>4.2.2<br>4.2.3<br>Active                                                                              | Useless TE substitutions                           | 54.<br>55<br>56<br>59<br>60<br>63                                     |

|   | 4.2  | <ul> <li>4.1.1</li> <li>4.1.2</li> <li>4.1.3</li> <li>Impro</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>Active</li> <li>4.3.1</li> </ul> | Useless TE substitutions                           | 54.<br>55<br>56<br>59<br>60<br>63<br>64                               |

|   | 4.2  | 4.1.1<br>4.1.2<br>4.1.3<br>Impro<br>4.2.1<br>4.2.2<br>4.2.3<br>Active<br>4.3.1<br>4.3.2                                                            | Useless TE substitutions                           | 54.<br>55<br>56<br>59<br>60<br>63<br>64<br>64                         |

|   | 4.2  | 4.1.1<br>4.1.2<br>4.1.3<br>Impro<br>4.2.1<br>4.2.2<br>4.2.3<br>Active<br>4.3.1<br>4.3.2<br>4.3.3                                                   | Useless TE substitutions                           | 54.<br>55<br>56<br>59<br>60<br>63<br>64<br>64<br>64<br>66<br>68       |

|   | 4.2  | 4.1.1<br>4.1.2<br>4.1.3<br>Impro<br>4.2.1<br>4.2.2<br>4.2.3<br>Active<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                          | Useless TE substitutions                           | 54.<br>55<br>56<br>59<br>60<br>63<br>64<br>64<br>64<br>66<br>68<br>69 |

| 4.5  | Summ                                                               | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

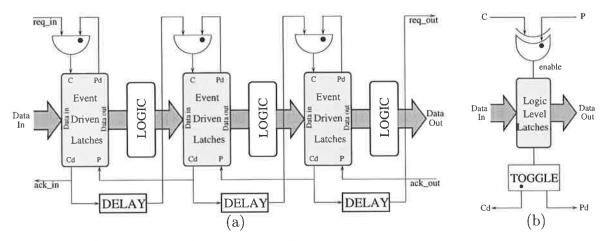

| Asy  | nchron                                                             | nous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | FIFO                                                               | pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.1.1                                                              | Micropipeline 2P FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

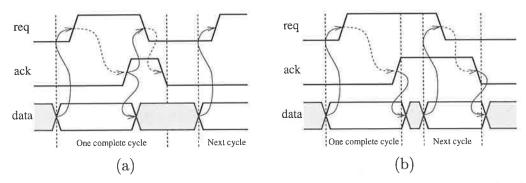

|      | 5.1.2                                                              | 4P FIFO circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

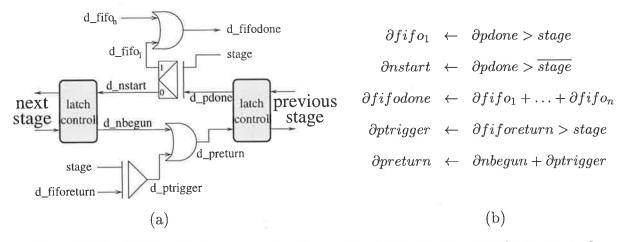

|      | 5.1.3                                                              | A fast ECS FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.1.4                                                              | Comparison of FIFO designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

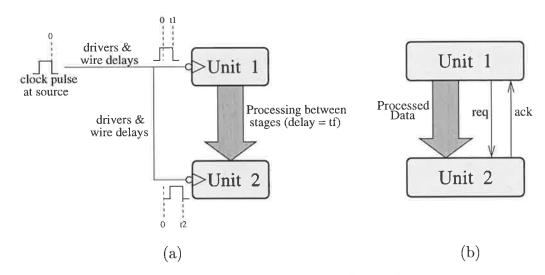

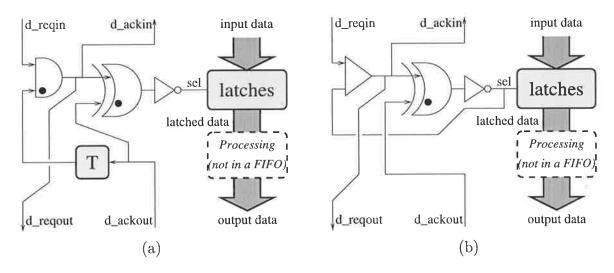

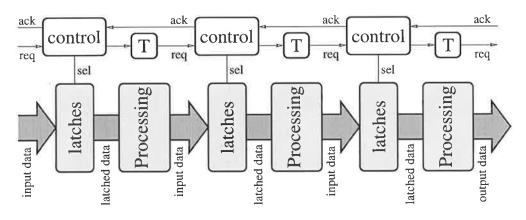

| 5.2  | Pipelin                                                            | nes with processing delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

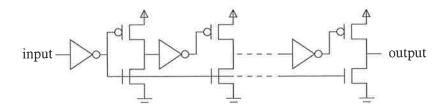

| 5.3  | Precha                                                             | arge pipelines: general concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

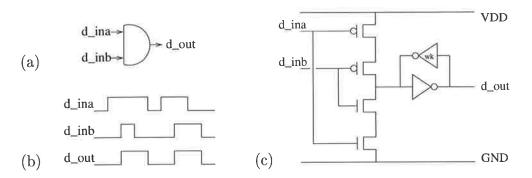

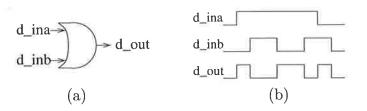

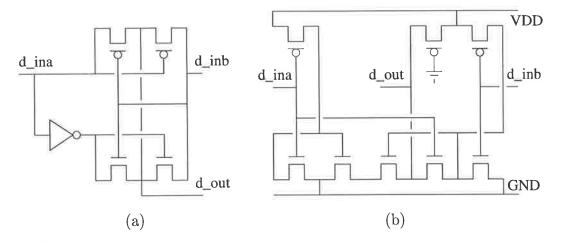

|      | 5.3.1                                                              | Dynamic Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.3.2                                                              | Requirements of a PP for dynamic logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

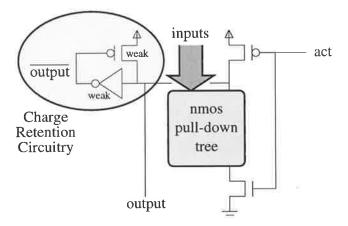

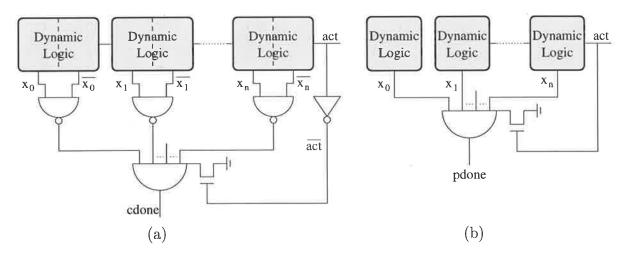

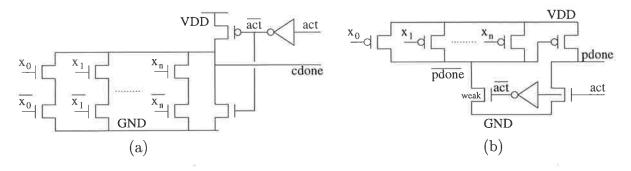

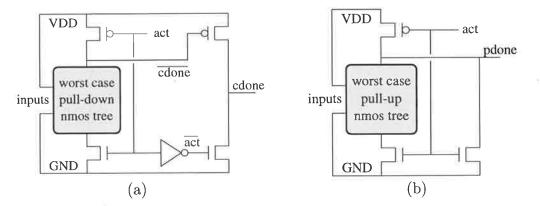

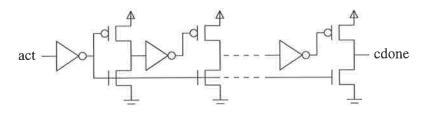

|      | 5.3.3                                                              | Methods of completion and precharge detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

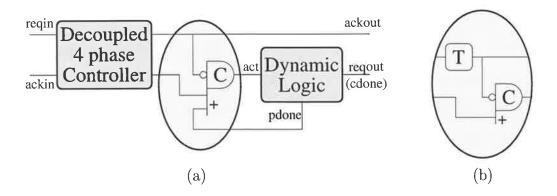

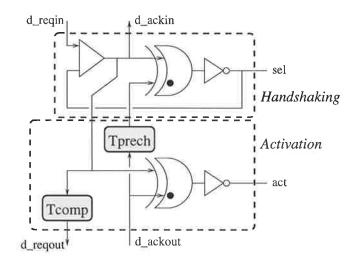

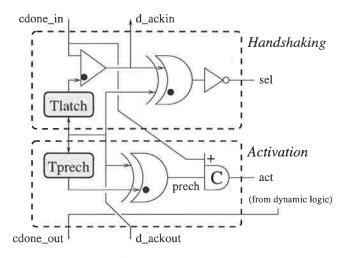

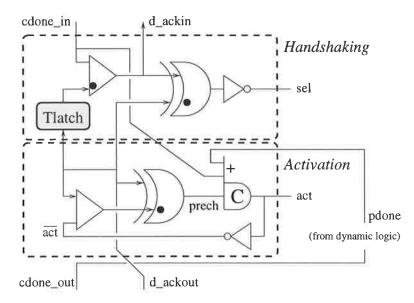

| 5.4  | Decou                                                              | pled 4P precharge pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.4.1                                                              | Implementations for $PP\alpha$ , $PP\beta$ , and $PP\gamma$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.4.2                                                              | Performance comparisons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.5  | ECS p                                                              | precharge pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.5.1                                                              | $PP\alpha$ implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.5.2                                                              | $\mathrm{PP}eta$ implementation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.5.3                                                              | $\mathrm{PP}\gamma$ implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.5.4                                                              | Performance comparisons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.6  | Comp                                                               | arison of ECS and D4P PP structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.7  | Summ                                                               | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Self | -Time                                                              | d Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 0                                                                  | о́ с                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 6.3.5                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | <b>Asy</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.5<br>5.6<br>5.7 | Asymptotic function         5.1         5.1         5.1.1         5.1.2         5.1.3         5.1.4         5.1.3         5.1.4         5.2         Pipelin         5.3         Precha         5.3.1         5.3.2         5.3.1         5.3.2         5.3.3         5.4         Decou         5.4.1         5.4.2         5.4.1         5.4.2         5.4.1         5.4.2         5.5.1         5.5.2         5.5.1         5.5.2         5.5.3         5.5.4         5.5.5         5.5.1         5.5.2         5.5.3         5.5.4         5.5.3         5.5.4         5.5.5         Strict         6.3         6.3.1         6.3.2         6.3.3         6.3.4 | Asynchronous Pipelines         5.1       FIFO pipelines         5.1.1       Micropipeline 2P FIFOs         5.1.2       4P FIFO circuits         5.1.3       A fast ECS FIFO         5.1.4       Comparison of FIFO designs         5.2       Pipelines with processing delays         5.3       Precharge pipelines: general concepts         5.3.1       Dynamic Logic         5.3.2       Requirements of a PP for dynamic logic         5.3.3       Methods of completion and precharge detection         5.4       Decoupled 4P precharge pipelines         5.4.1       Implementations for PP $\alpha$ , PP $\beta$ , and PP $\gamma$ 5.4.2       Performance comparisons         5.5       ECS precharge pipelines         5.5.1       PP $\alpha$ implementation         5.5.2       PP $\beta$ implementation         5.5.3       PP $\gamma$ implementation         5.5.4       Performance comparisons         5.6       Comparison of ECS and D4P PP structures         5.7       Summary         5.8       Comparison of ECS and D4P PP structures         6.1       Strict self-timing requirements         6.2       Designing and utilizing self-timed units         6.3       Adder Structures         6 |

|   |     | 6.3.6  | PST ripple select implementation                       |

|---|-----|--------|--------------------------------------------------------|

|   |     | 6.3.7  | Comparison of PST and ST adders                        |