ADELAIDE UNIVERSITY

Department of Electrical and Electronic Engineering

## Multiport Memory as a Medium for Interprocessor Communication in Multiprocessors

By

### Nasser Asgari

B.Sc., M.Sc.

Thesis submitted for the degree of

Doctor of Philosophy

February 2003

### Abstract

The performance of a multiprocessor greatly depends on the effectiveness of its interprocessor communication. Shared memory and message passing are two major communication architectures for multiprocessors. In shared memory systems, processors communicate by writing to and reading from a common memory. In message passing architectures, nodes communicate by passing messages through an interconnection network using send and receive commands. Both systems have their advantages and disadvantages. This study aims to explore the feasibility of using multiport memories for interprocessor communication based on message passing.

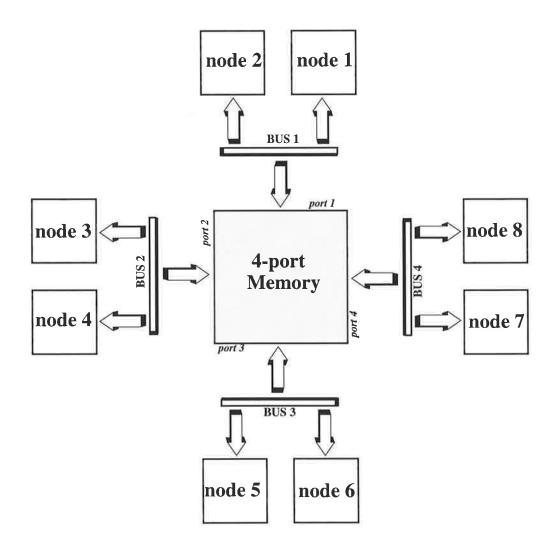

The individual ports of a multiport memory provide independent access to memory cells and can be used as communication links. In the communication structure proposed in this study, several nodes connected to a multiport memory can communicate in parallel without the overhead and delay of the bus architecture, or the interconnection network of a typical shared memory system. The small number of ports on multiport memory is a limiting factor that restricts the number of nodes connected to this structure.

The proposed structure can be scaled by using a hierarchy in which the nodes that are not connected directly can communicate through network controllers and other available multiport memories. In this structure, shared memory is used as a link for message passing. In contrast to other shared memory systems, the small shared memory in this structure is exclusively used for communication purpose.

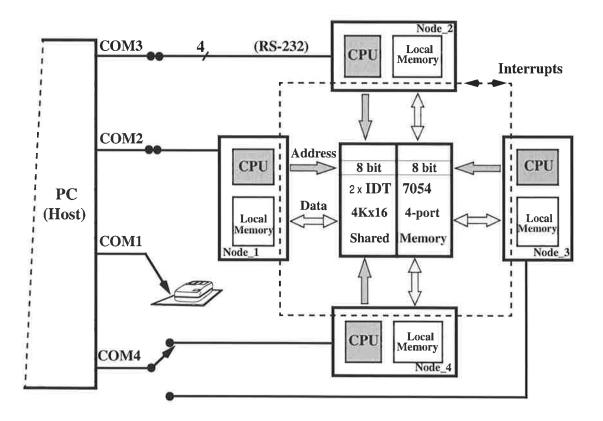

The first stage in evaluating the proposed structure was the design and implementation of a small multiprocessor called MultiCom. In this prototype system, four nodes were interconnected by a 4-port memory. The memory management of MultiCom could prevent the nodes from interfering with each other using static and dynamic allocations. In particular, dynamic allocation used fewer but larger buffers that could be assigned to any communication on demand, and full memory utilization was possible. It could also handle multicasting and broadcasting very efficiently. As dynamic allocation required a lock mechanism for allocating the buffers, in the absence of hardware locks on multiport memories, two new software locks for controlling the ownership of the multiport memory were designed and successfully tested. Using a basic communication protocol for MultiCom, the measured communication rate was 4.2 times faster than a system using serial links, 11 times faster than a system using dual-port memories, and 14 times better than a bus-based system. In addition, compared to a system using dual-port memories, the system enjoyed a four-fold reduction in cost.

A simulation model was designed to evaluate the performance of the scaled structure. The model showed that the structure was scalable for small systems in which all of the nodes were connected as a group using a single multiport memory. It also confirmed that the structure only required small amount of shared memory for message passing. However, the performance of the cluster structure in the original proposal in which several groups were connected using a network controller was not desirable. The communication rate dropped considerably under high inter-group message transfers because of the overloaded network controller. To overcome this problem, the cluster structure was modified and separate network controllers were used for each group. In addition, an extra multiport memory was used to interconnect the network controllers. With this modification, the performance of a cluster was significantly improved and overloading of the network controllers was considerably reduced. The structure of a network of clusters was also improved to accommodate the modified cluster structure, and other measures were implemented to reduce the load of network controllers. The improved structure can be used for medium to large-scale systems.

## **Statement of Originality**

This work contains no material which has been accepted for the award of any degree or diploma in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text.

The author hereby consents to this copy of the thesis, when deposited in the University Library, being available for loan or photocopying.

Nasser Asgari

February 2003

### Acknowledgments

I would like to express my gratitude to Professor Neil Burgess, my supervisor, for his continual help and support. His guidance, criticism, and encouragement were valuable sources of motivation for me in undertaking this research.

My sincere thanks to Mr Michael Liebelt, my second supervisor who was always available for discussion at any stage. He was the one to rely on when everything else failed.

I would like to acknowledge the efforts of my wife Shiva and my daughters Kimiya and Hasti for providing me a suitable environment to work on this research. I am thankful of their companionship, support, and understanding when much of my time was spent on studying.

I would also like to thank the Ministry of Culture and Higher Education of Iran for providing me the opportunity and support to undertake this research.

### To Shiva, Kimiya, and Hasti

The loves of my life.

### Contents

| Abstract                 | i     |

|--------------------------|-------|

| Statement of Originality | iii   |

| Acknowledgments          | iv    |

| Contents                 | vi    |

| List of Figures          | xiv   |

| List of Tables           | xviii |

| List of Publications     | xix   |

1

### CHAPTER 1 Introduction

| 1       | Background and motivation                             | 2  |

|---------|-------------------------------------------------------|----|

| 2       | Objectives and scope of the study                     | 4  |

| 3       | Contributions                                         | 4  |

|         | 3.1 Communication structure                           | 5  |

|         | 3.2 Multiport memory management                       | 5  |

|         | 3.3 Communication protocols                           | 6  |

|         | 3.4 Support circuits for multiport memory             | 6  |

| 4       | Thesis structure                                      | 6  |

|         | 4.1 Background                                        | 7  |

|         | 4.2 Interprocessor communication                      | 7  |

|         | 4.3 Multiport memory for interprocessor communication | 7  |

|         | 4.4 Hardware model                                    | 7  |

|         | 4.5 Memory management                                 | 8  |

|         | 4.6 Simulation model                                  | 8  |

|         | 4.7 Improved communication structure                  | 8  |

|         | 4.8 Further directions                                | 8  |

|         | 4.9 Structure of multiport memory                     | 9  |

| CHAPTER | 2 Interprocessor Communication                        | 10 |

| 1 | Introduction                        | 11 |

|---|-------------------------------------|----|

| 2 | Shared memory                       | 11 |

|   | 2.1 Shared memory with a single bus | 12 |

|   | 2.2 Interleaved shared memory       | 13 |

|   | 2.2.1 Multiple-bus shared memory    | 13 |

|   | 2.2.2 Crossbar switch               | 14 |

| 2.2.3 Multistage network               | 16 |

|----------------------------------------|----|

| 3 Message passing                      | 18 |

| 3.1 Network topologies                 | 18 |

| 3.1.1 Static topologies                | 19 |

| 3.1.2 Dynamic topologies               | 24 |

| 3.2 Interconnection methods            | 25 |

| 3.2.1 Serial links                     | 25 |

| 3.2.2 Parallel links                   | 25 |

| 3.2.3 Dual-port memory                 | 26 |

| 4 Convergence                          | 30 |

| 5 Shared memory using multiport memory | 32 |

| 6 Conclusion                           | 34 |

### CHAPTER 3 Multiport Memory for Interprocessor Communication

| 1 Multiport memory: background and previous work      | 36 |

|-------------------------------------------------------|----|

| 1.1 Multiport memory design                           | 36 |

| 1.2 Innovative structures for multiport memory        | 38 |

| 1.3 Application of multiport memory                   | 39 |

| 1.3.1 Processor design                                | 39 |

| 1.3.2 Special purpose systems                         | 41 |

| 1.3.3 Communication                                   | 42 |

| 2 Proposed structure for interprocessor communication | 43 |

| 2.1 Communication in a group                          | 44 |

| 2.2 Communication in a cluster                        | 45 |

| 2.3 Communication in a network                        | 47 |

| 3 Verifying the structure                             | 49 |

35

| 5 Cor     | nclusion               |

|-----------|------------------------|

| CHAPTER 5 | Memory Management and  |

|           | Communication Protocol |

# Communication Protocol

54

55

55

60

60

62

64

64

65

68

**69**

70

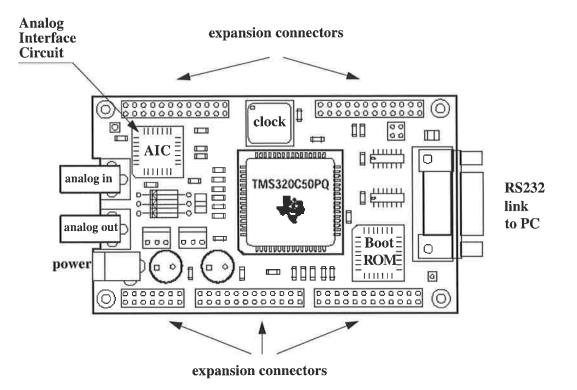

1 Hardware design 1.1 Nodes .....

### 3.1 MultiCom, a hardware prototype. 49 49 3.2 Simulation model 4.1 Availability of multiport memory ..... 50 4.2 Pinout of multiport memory..... 51 4.3 Overloading of network controller 52

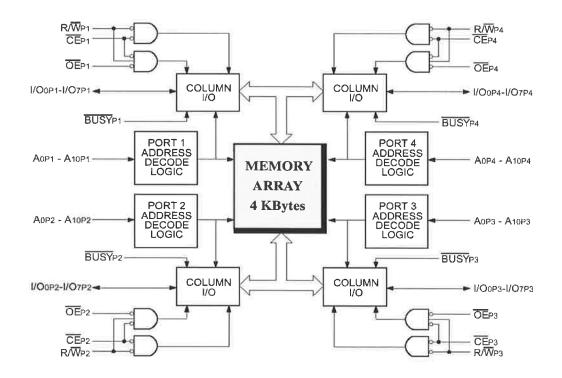

1.2 Four-port memory ...... 57

2 Programming

2.1 Synchronization

2.2 Test program.....

**3** Buffer allocation

4 Results and discussion

4.1 Comparison of results .....

1 Memory management 70

1.1 Static allocation....

MultiCom: A Hardware Model

**CHAPTER 4**

#### Contents

| 1.2 Dynamic allocation 72                           | 2  |

|-----------------------------------------------------|----|

| 1.3 Multicast / broadcast                           | 3  |

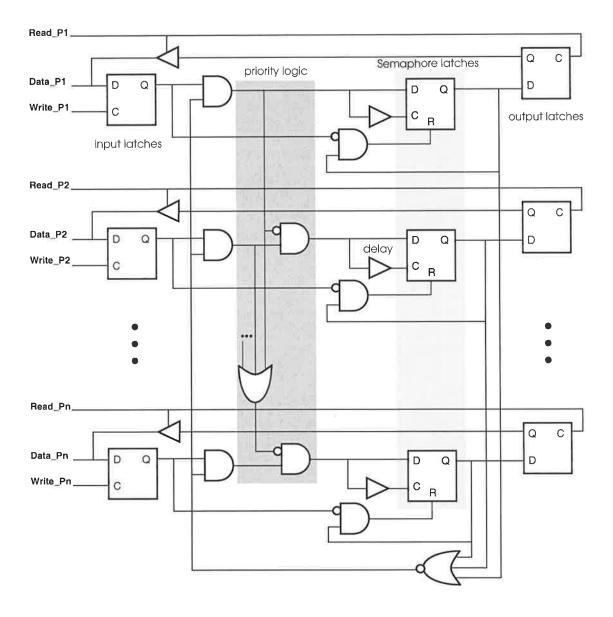

| <b>2</b> Semaphore signalling                       | 4  |

| 2.1 Hardware semaphore                              | 4  |

| 2.2 Software semaphore                              | 7  |

| 2.2.1 TOKEN passing                                 | 9  |

| 2.2.2 Waiting list 8                                | 0  |

| 2.2.3 Lock with BUSY 8                              | 2  |

| 2.2.4 Fast lock                                     | 5  |

| <b>3</b> Communication protocol                     | 8  |

| 3.1 Basic communication protocol 89                 | 9  |

| 3.2 Protocol for dynamic allocation                 | 2  |

| 3.3 Protocol for multicast / broadcast              | 6  |

| 4 Results from MultiCom 100                         | 0  |

| 4.1 Details of data transfer                        | 0  |

| 4.2 Results of static allocation 10                 | 1  |

| 4.3 Results of dynamic allocation 102               | 3  |

| 4.4 Results of multicasting/broadcasting 10         | 5  |

| 4.5 Comparison of results 10'                       | 7  |

| 4.5.1 Comparison to a bus-based system              | 17 |

| 4.5.2 Comparison to a system using dual-port memory | 18 |

| 4.5.3 Comparison to serial links 10                 | 9  |

| 5 Discussion 110                                    | 0  |

| 5.1 Improving the performance 11                    | 1  |

| 5.1.1 Increasing the speed of nodes 11              | 1  |

| 5.1.2 Use of wider datapath 11                      | 1  |

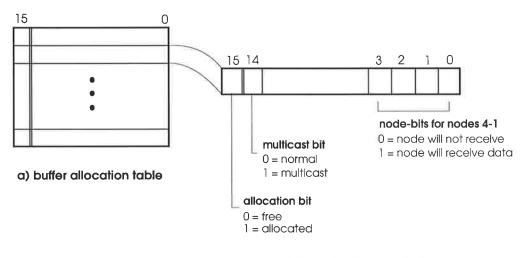

| 5.2 Structure of the allocation table 112           | 2  |

| 6 Conclusion 114                                    | 4  |

### CHAPTER 6 Simulation Modelling

| 1 | 1 | 7 |

|---|---|---|

|   |   |   |

| 1 Simulation model                          | 118 |

|---------------------------------------------|-----|

| 2 Structure of simulation model             | 118 |

| 2.1 Node module                             | 119 |

| 2.2 Multiport memory module                 | 119 |

| 2.3 Network controller module               | 120 |

| 2.4 Log file                                | 120 |

| 3 Simulation stages                         | 121 |

| 3.1 Simulation of MultiCom                  | 121 |

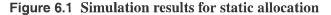

| 3.1.1 Static allocation                     | 122 |

| 3.1.2 Dynamic allocation                    | 123 |

| 3.2 Simulation of a larger group            | 125 |

| 3.3 Simulation of a cluster of groups       | 129 |

| 3.3.1 Communication protocol in a cluster   | 130 |

| 3.3.2 Header of a packet                    | 133 |

| 3.3.3 Results                               | 133 |

| 3.4 Simulation model for the entire network | 137 |

| 4 Discussion                                | 137 |

| 4.1 Group structure                         | 138 |

| 4.2 Overloaded network controller           | 139 |

| 5 Conclusion                                | 140 |

### CHAPTER 7 Improved Communication Structure 142

| 1 | Improved cluster structure  | 143 |

|---|-----------------------------|-----|

| 2 | Modified network structure  | 147 |

| 3 | Improved network structure. | 151 |

| 4 | Discussion                   | 158 |

|---|------------------------------|-----|

|   | 4.1 Scaling of the structure | 158 |

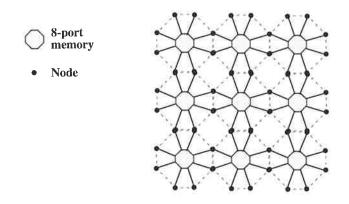

|   | 4.2 Use of 8-port memories   | 158 |

|   | 4.3 Practical issues         | 159 |

| 5 | Conclusion                   | 160 |

### CHAPTER 8 Conclusion and Further Directions 162

| 1 | Con                | clusions                                             | 163 |

|---|--------------------|------------------------------------------------------|-----|

| 2 | 2 Further research |                                                      | 166 |

|   | 2.1                | Hardware support for multiport memory                | 166 |

|   |                    | 2.1.1 Multiport semaphore logic                      | 167 |

|   |                    | 2.1.2 Centralized control.                           | 167 |

|   | 2.2                | Use of DMA for data transfer                         | 168 |

|   | 2.3                | Using different communication structure              | 169 |

|   |                    | 2.3.1 Mesh structure                                 | 169 |

|   |                    | 2.3.2 Increasing the port count of multiport memory. | 170 |

### APPENDIXStructure of Multiport Memory172

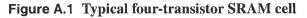

| 1 Structure of single-port memory                  | 173 |

|----------------------------------------------------|-----|

| 2 Structure of dual-port memory                    | 175 |

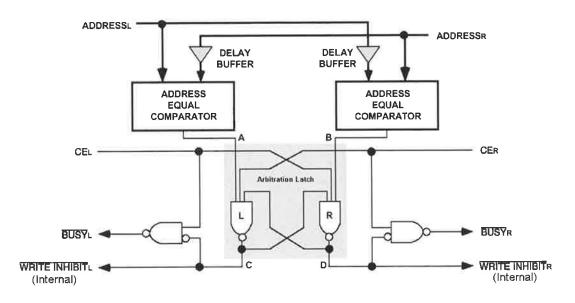

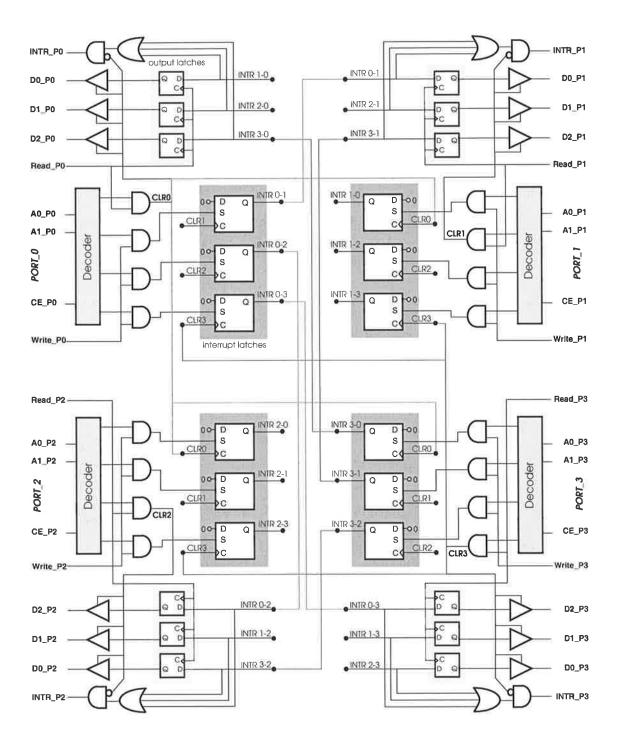

| 2.1 Control logic for dual-port memory             | 176 |

| 2.1.1 Busy logic for simultaneous access conflicts | 177 |

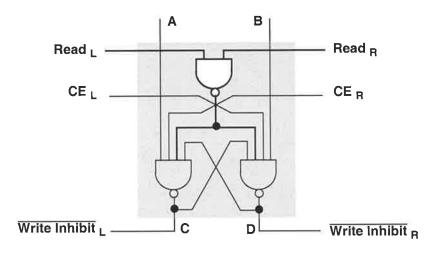

| 2.1.2 Semaphore logic                              | 179 |

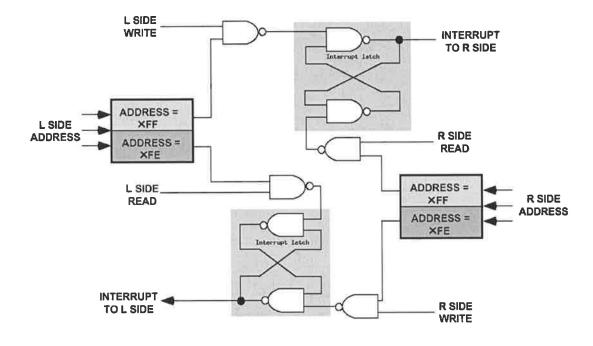

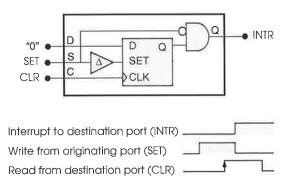

| 2.1.3 Interrupt logic for signalling               | 180 |

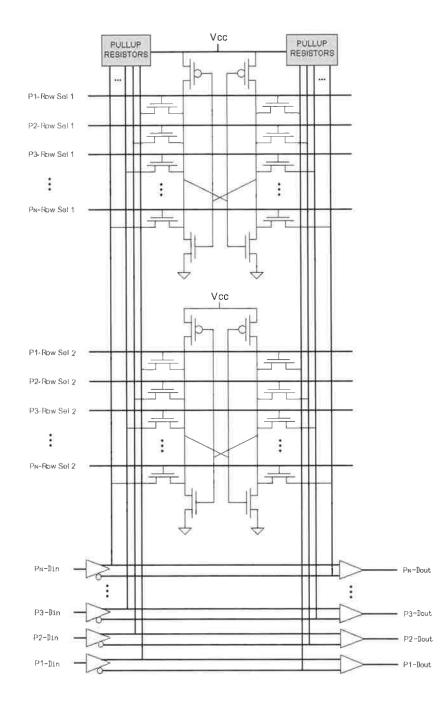

| 3 Structure of multiport memory                    | 181 |

| 4 Discussion                                       | 182 |

|   | 4.1 | Limited capacity                   | 182 |

|---|-----|------------------------------------|-----|

|   | 4.2 | Large number of pinout             | 184 |

|   | 4.3 | Control logic for multiport memory | 184 |

|   |     | 4.3.1 Busy logic                   | 184 |

|   |     | 4.3.2 Semaphore logic              | 185 |

|   |     | 4.3.3 Interrupt logic              | 186 |

|   | 4.4 | Simultaneous read of a cell        | 190 |

| 5 | Sun | nmary                              | 190 |

### Bibliography

**192**

## **List of Figures**

| Figure 2.1  | Simple shared memory                             | 12 |

|-------------|--------------------------------------------------|----|

| Figure 2.2  | Interleaved memory                               | 14 |

| Figure 2.3  | Multiple-bus shared memory                       | 15 |

| Figure 2.4  | Crossbar switch                                  | 16 |

| Figure 2.5  | Multistage network                               | 17 |

| Figure 2.6  | Ring topology                                    | 19 |

| Figure 2.7  | Mesh or grid topology                            | 20 |

| Figure 2.8  | Ring-mesh topology                               | 21 |

| Figure 2.9  | 32-node hypercube (5-cube) with all of its links | 22 |

| Figure 2.10 | 64-node hypercube (6-cube)                       | 22 |

| Figure 2.11 | 512 node hypercube (9-cube)                      | 23 |

| Figure 2.12 | Ring topology with dynamic links                 | 24 |

| Figure 2.13 | Dual-port memory                                 | 26 |

| Figure 2.14 | Restricted Shared Memory (RSM) architecture for  |    |

|             | communication through dual-port memories         | 27 |

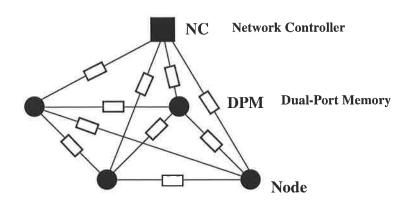

| Figure 2.15 | Using DPM to connect nodes in a cube                   | 28 |

|-------------|--------------------------------------------------------|----|

| Figure 2.16 | Extending the structure using DPMs to 64 nodes         | 29 |

| Figure 2.17 | Another view of RSM architecture                       | 30 |

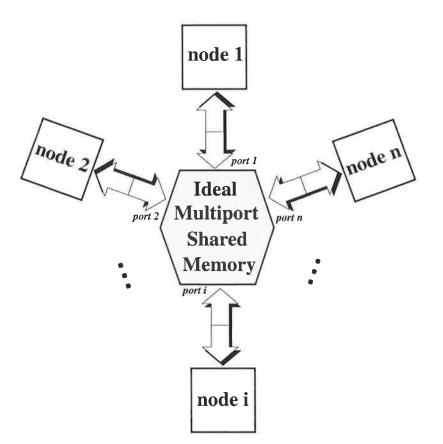

| Figure 2.18 | Multiport shared memory                                | 33 |

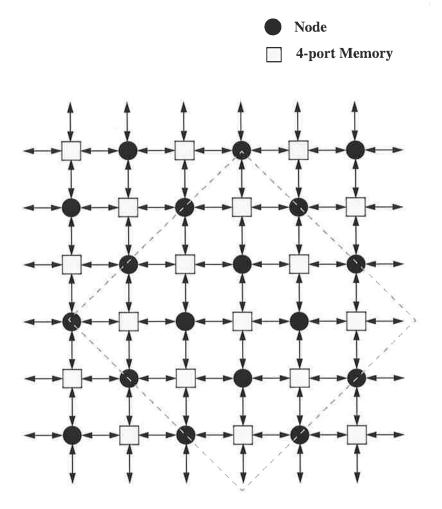

| Figure 3.1  | Communication in a grid with 4-port memory             | 43 |

| Figure 3.2  | Communication with multiport memory in a group         | 44 |

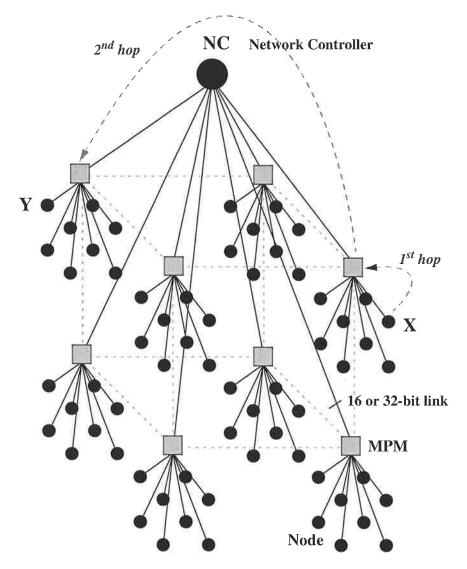

| Figure 3.3  | Communication in a cluster                             | 46 |

| Figure 3.4  | Communication in a network                             | 48 |

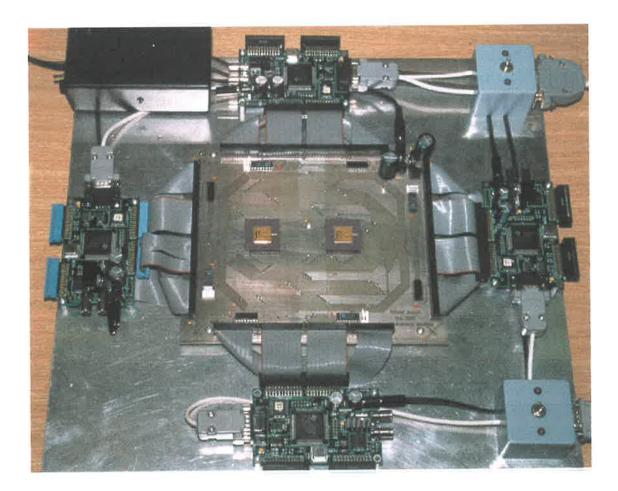

| Figure 4.1  | DSK as nodes of MultiCom                               | 56 |

| Figure 4.2  | IDT7054 four-port RAM                                  | 57 |

| Figure 4.3  | The block diagram of MultiCom                          | 58 |

| Figure 4.4  | The board designed for MultiCom                        | 59 |

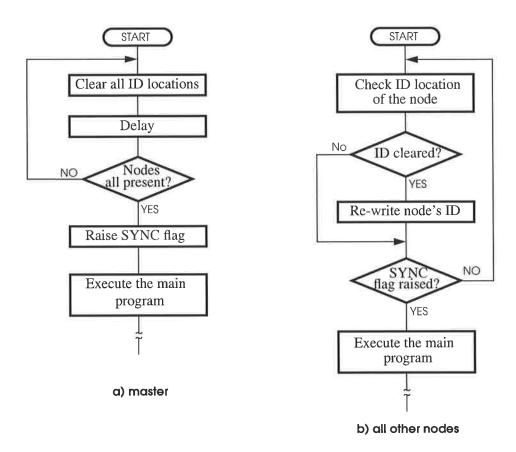

| Figure 4.5  | Synchronization algorithm                              | 61 |

| Figure 4.6  | All-to-all test program for MultiCom                   | 62 |

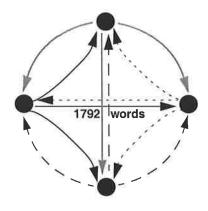

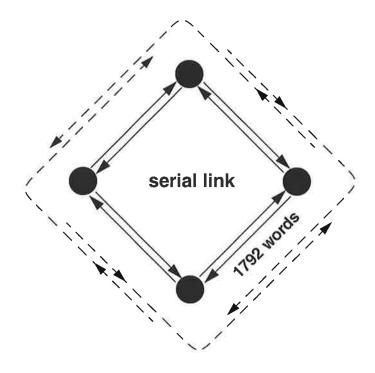

| Figure 4.7  | Serial communication of four nodes in 2-cube structure | 66 |

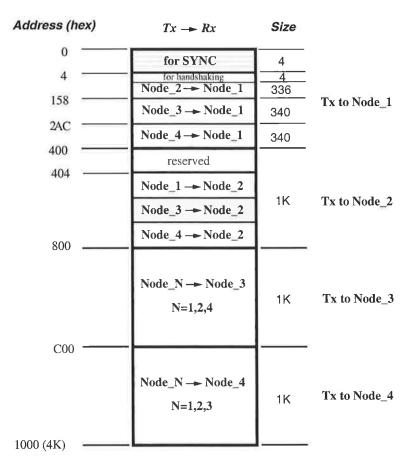

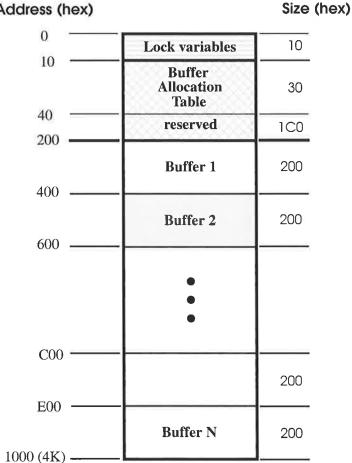

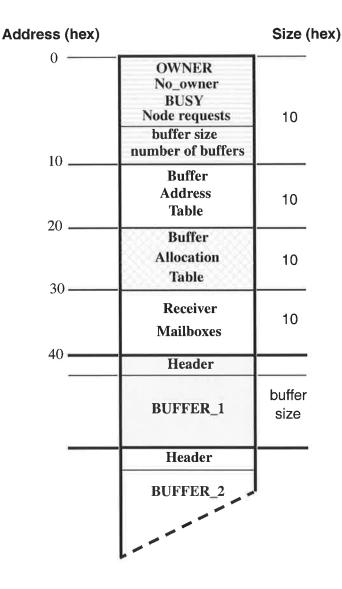

| Figure 5.1  | Memory map of MultiCom for static allocation           | 71 |

| Figure 5.2  | A typical memory layout for dynamic allocation         | 73 |

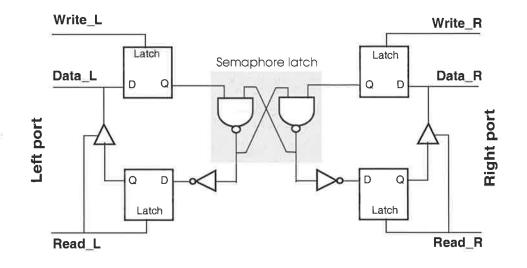

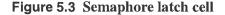

| Figure 5.3  | Semaphore latch cell                                   | 76 |

| Figure 5.4  | Waiting list                                           | 80 |

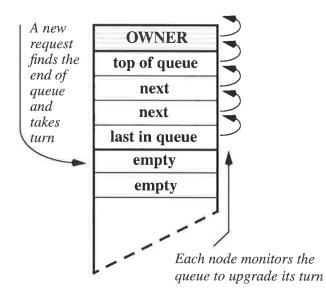

| Figure 5.5  | Lock with BUSY                                         | 83 |

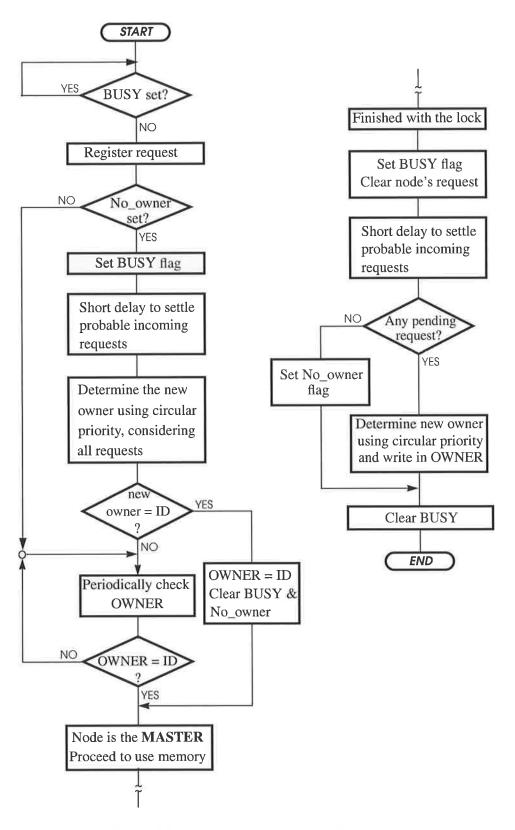

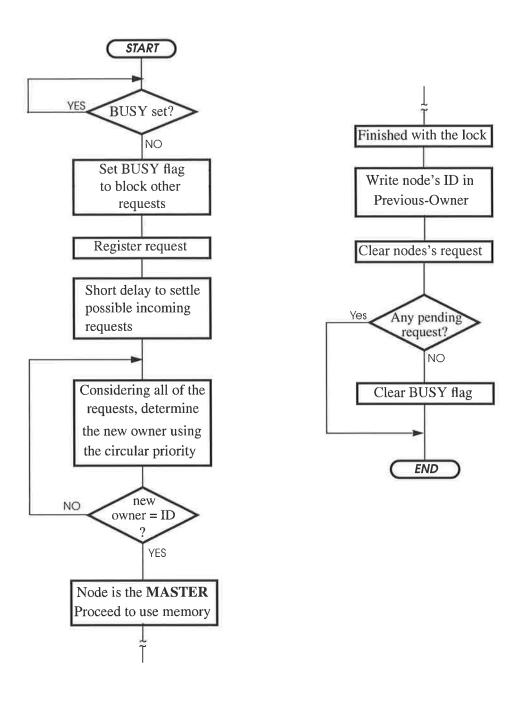

| Figure 5.6  | Flow chart of the lock with BUSY                       | 84 |

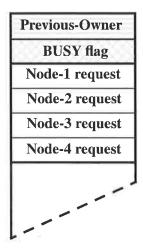

| Figure 5.7  | The fast lock                                          | 86 |

| Figure 5.8  | Flow chart of the fast lock                            | 87 |

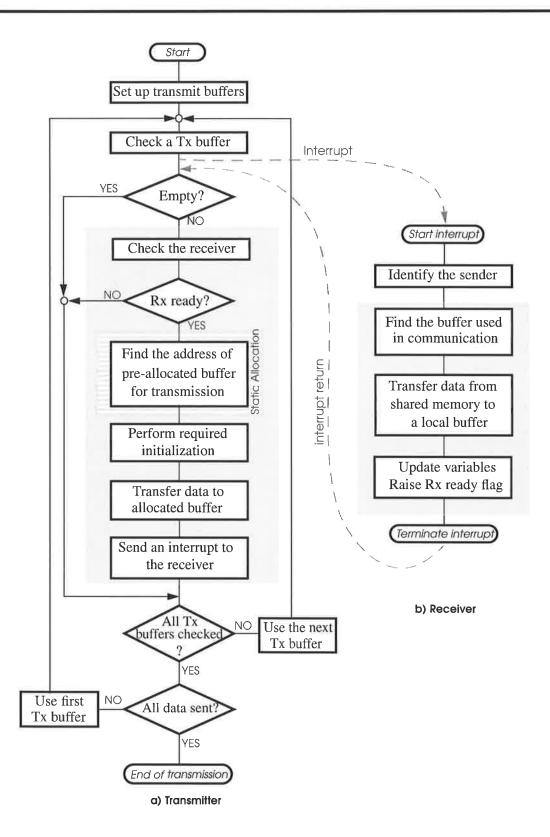

| Figure 5.9  | Basic communication protocol                           | 90 |

| Figure 5.10 | Memory map of MultiCom for dynamic allocation          | 93 |

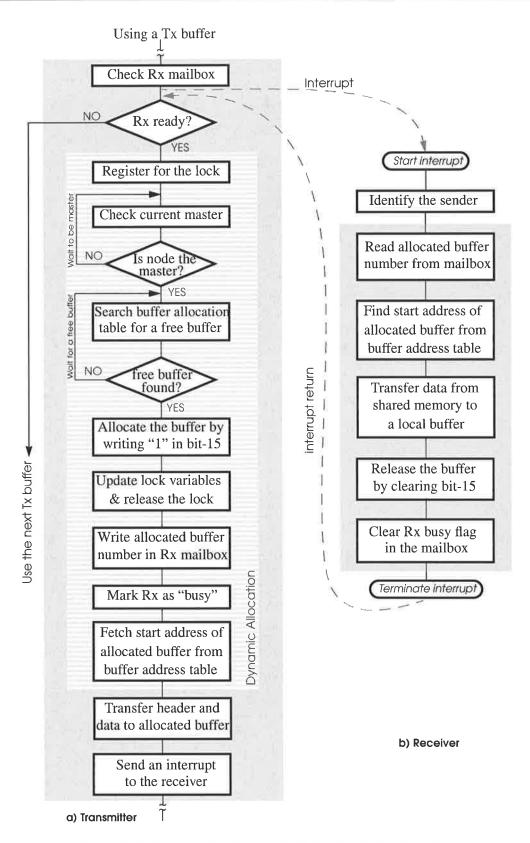

| Figure 5.11 | Communication protocol for dynamic allocation            | 94  |

|-------------|----------------------------------------------------------|-----|

| Figure 5.12 | The structure of buffer allocation table                 | 96  |

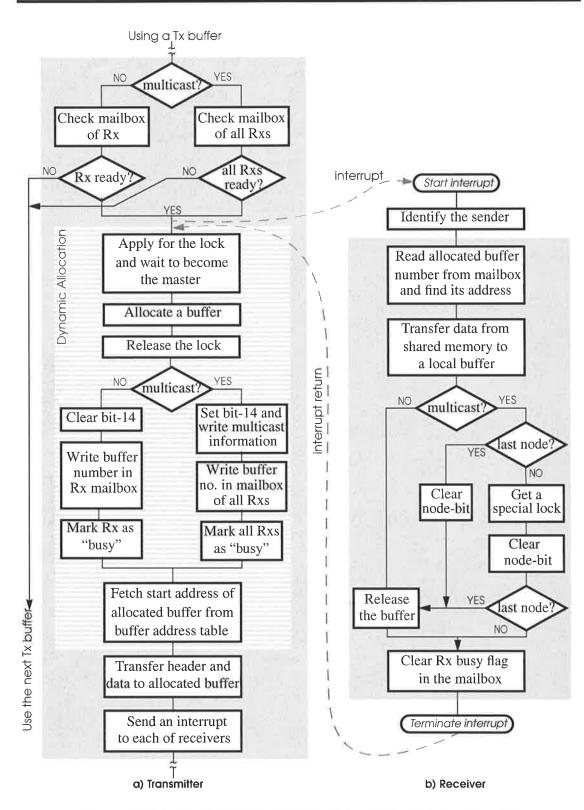

| Figure 5.13 | Communication protocol using multicasting/broadcasting   | 98  |

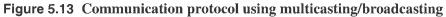

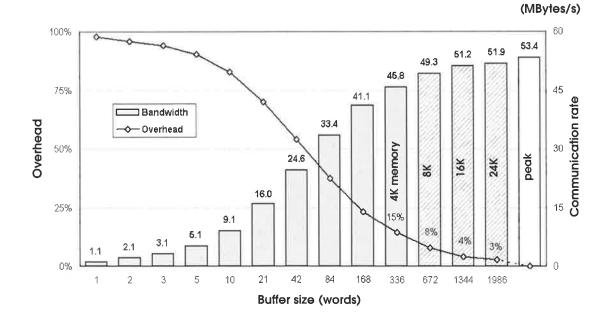

| Figure 5.14 | Effect of buffer size on communication rate and overhead |     |

|             | in static allocation                                     | 102 |

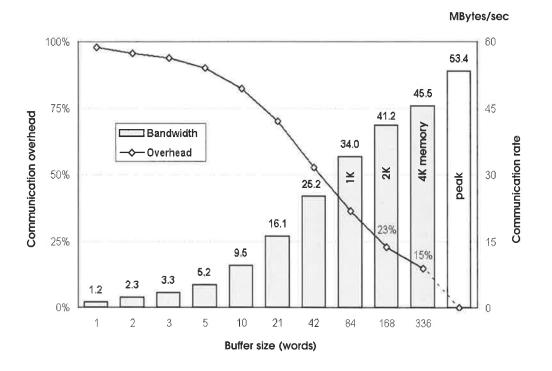

| Figure 5.15 | Communication rate for dynamic allocation                | 104 |

| Figure 5.16 | Results of broadcasting                                  | 106 |

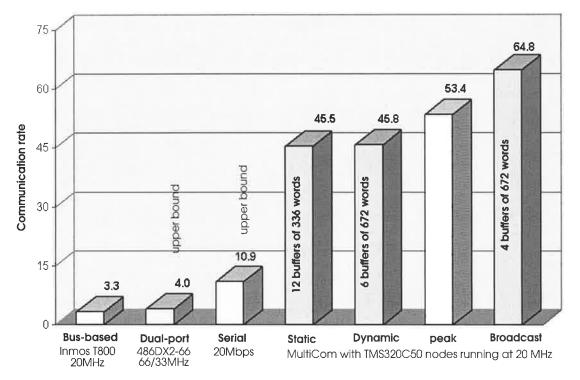

| Figure 5.17 | Comparison of results                                    | 110 |

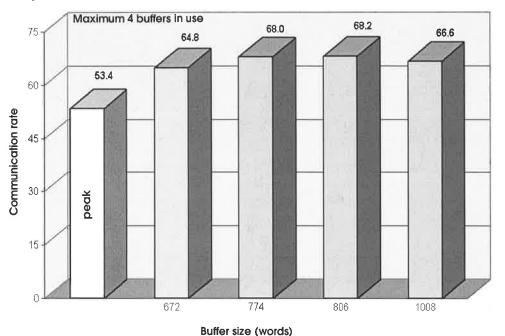

| Figure 6.1  | Simulation results for static allocation                 | 123 |

| Figure 6.2  | Simulation results for dynamic allocation                | 124 |

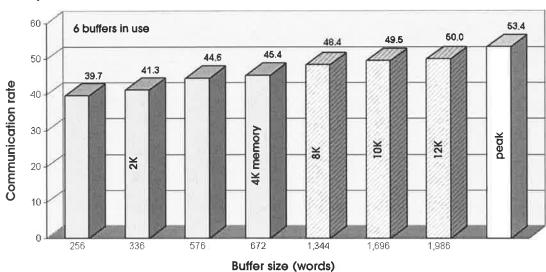

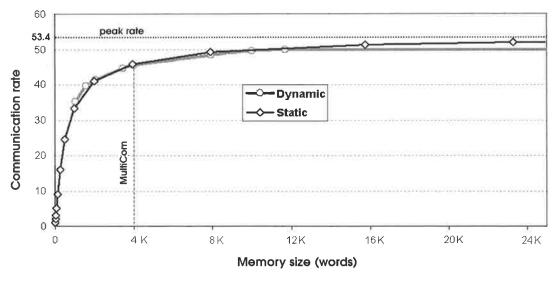

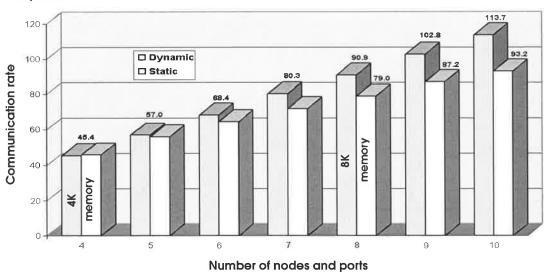

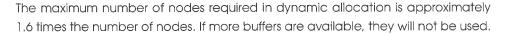

| Figure 6.3  | Effect of memory size in static and dynamic allocations  | 125 |

| Figure 6.4  | Scaling in a group                                       | 126 |

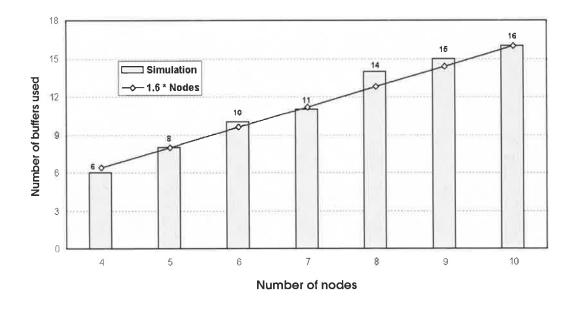

| Figure 6.5  | Number of buffers used in dynamic allocation             | 127 |

| Figure 6.6  | Static and dynamic allocations with fixed memory size    | 128 |

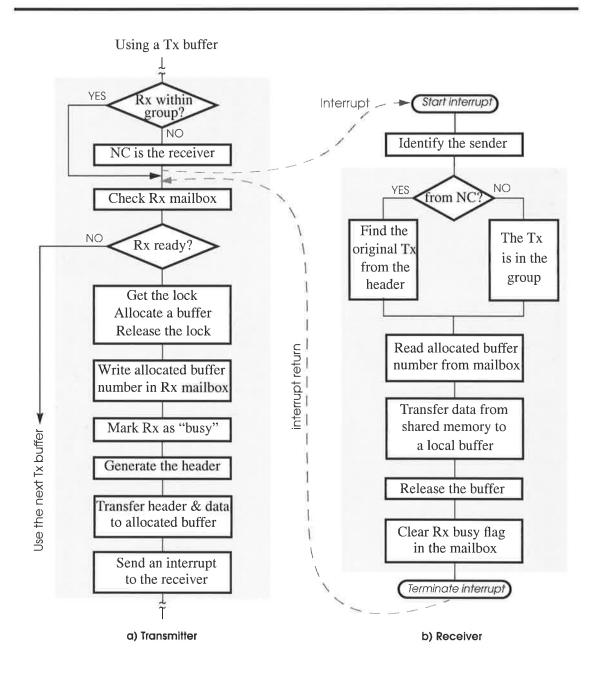

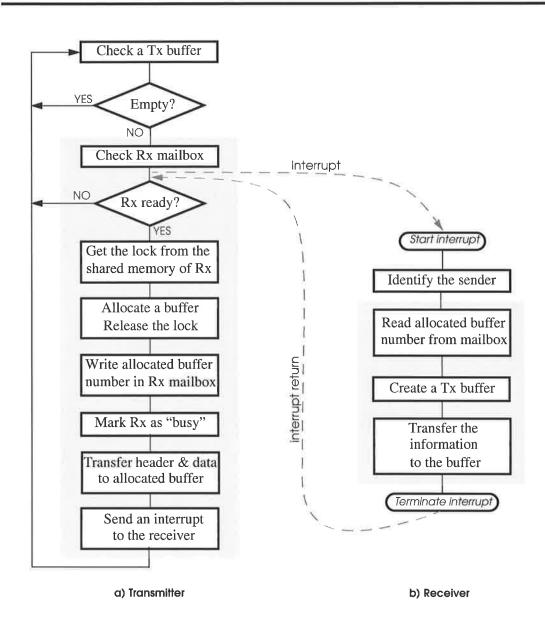

| Figure 6.7  | Communication protocol for a cluster                     | 131 |

| Figure 6.8  | Communication protocol for the NC of a cluster           | 132 |

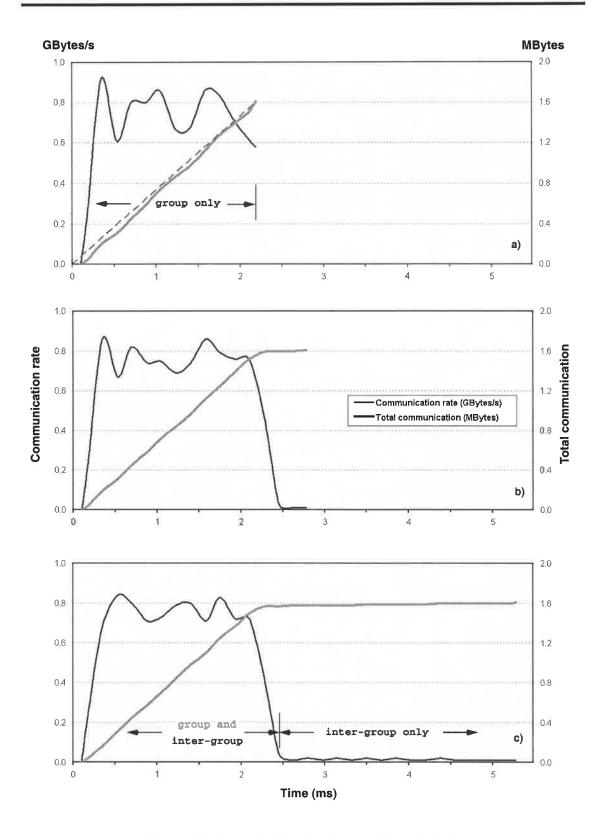

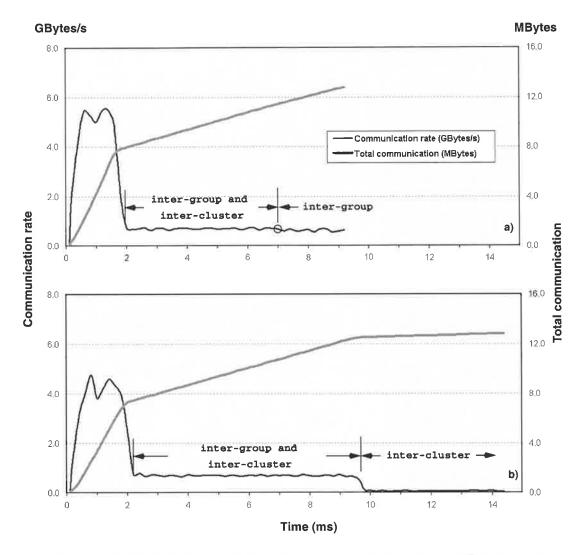

| Figure 6.9  | Communication of groups in a cluster                     | 134 |

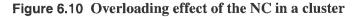

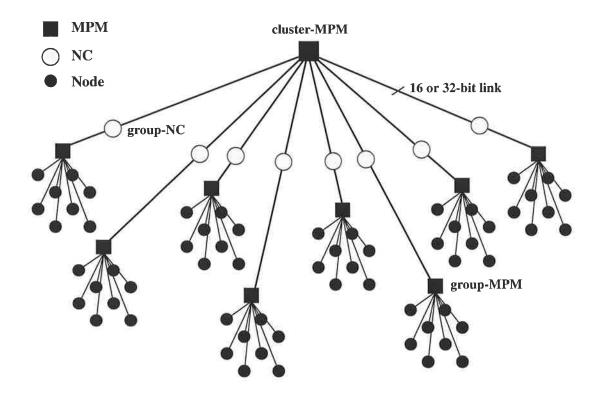

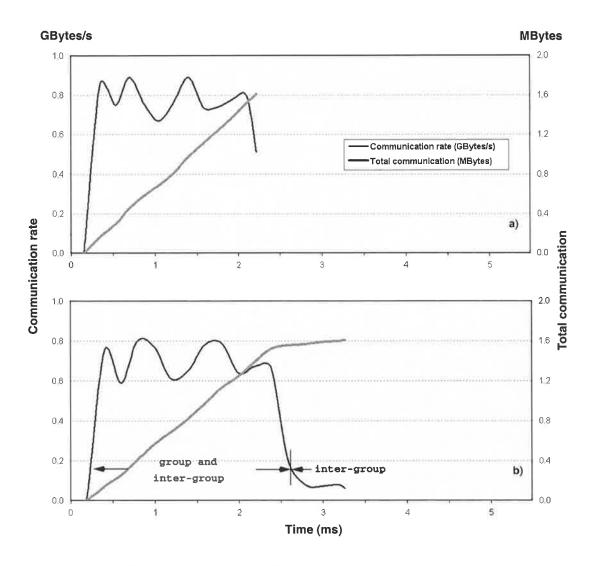

| Figure 6.10 | Overloading effect of the NC in a cluster                | 136 |

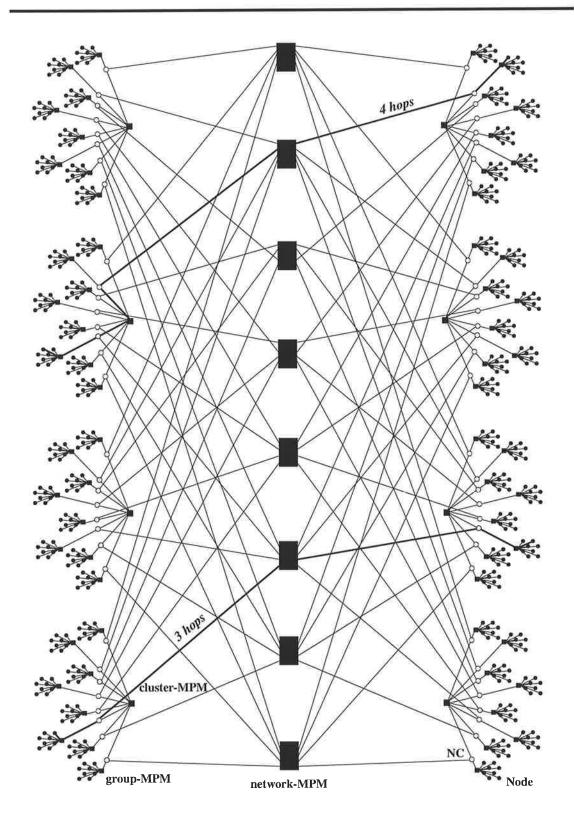

| Figure 7.1  | Improved cluster structure                               | 143 |

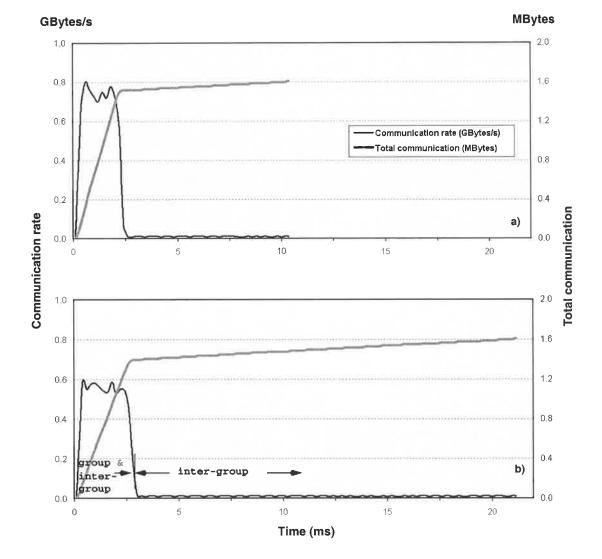

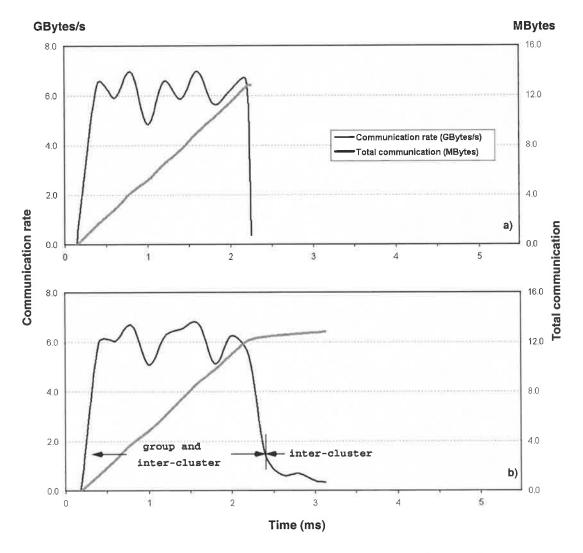

| Figure 7.2  | Communication of groups in improved cluster              | 144 |

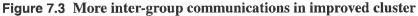

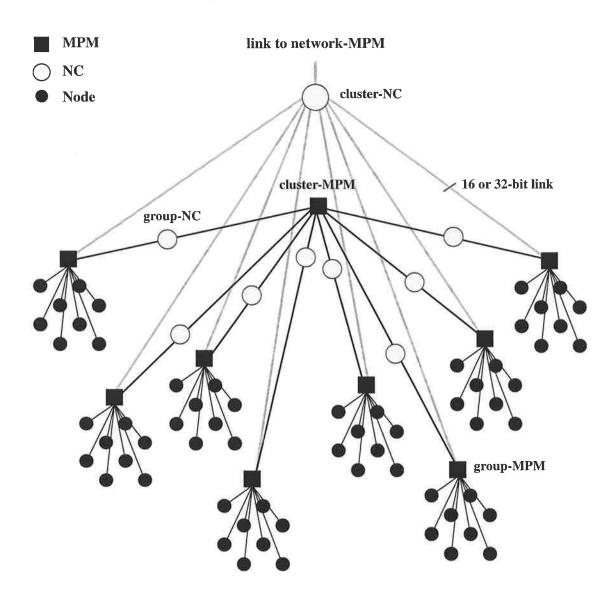

| Figure 7.3  | More inter-group communications in improved cluster      | 146 |

| Figure 7.4  | Modified cluster for a network                           | 147 |

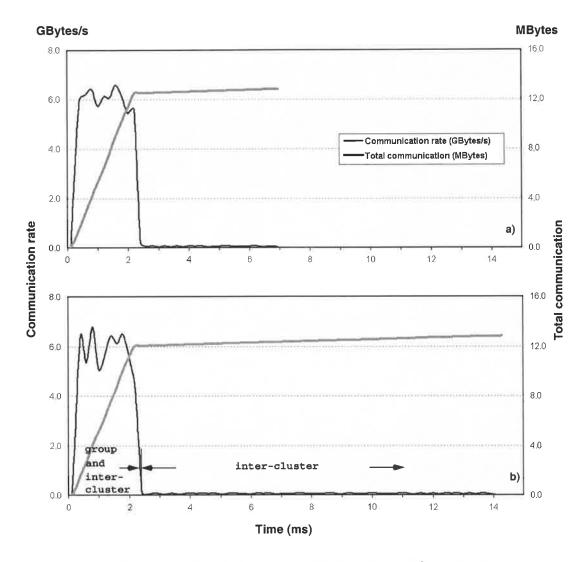

| Figure 7.5  | Inter-cluster communications in modified network         | 149 |

| Figure 7.6  | Inter-cluster and inter-group communications in          |     |

|             | modified network                                         | 150 |

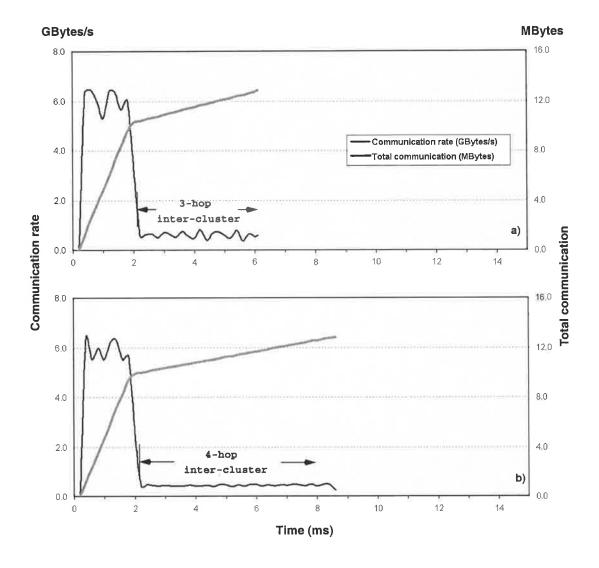

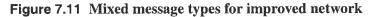

| Figure 7.7  | Improved network structure                                               | 152 |

|-------------|--------------------------------------------------------------------------|-----|

| Figure 7.8  | Inter-cluster communications in improved network                         | 153 |

| Figure 7.9  | Effect of extra hop for inter-cluster communications in improved network | 154 |

| Figure 7.10 | Inter-cluster and inter-group communications in improved network         | 155 |

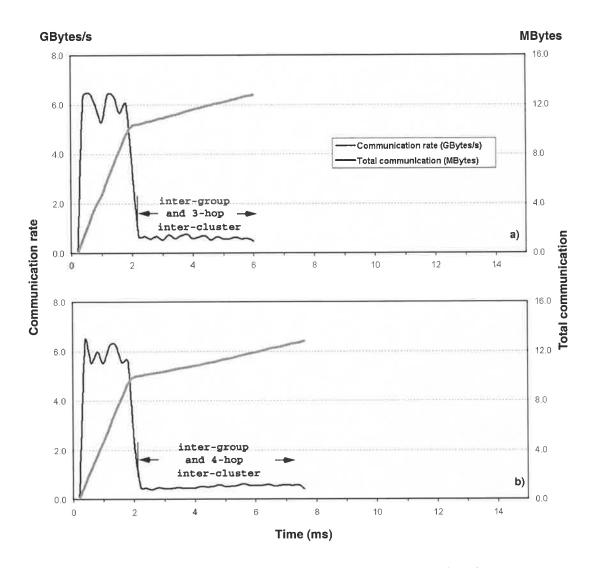

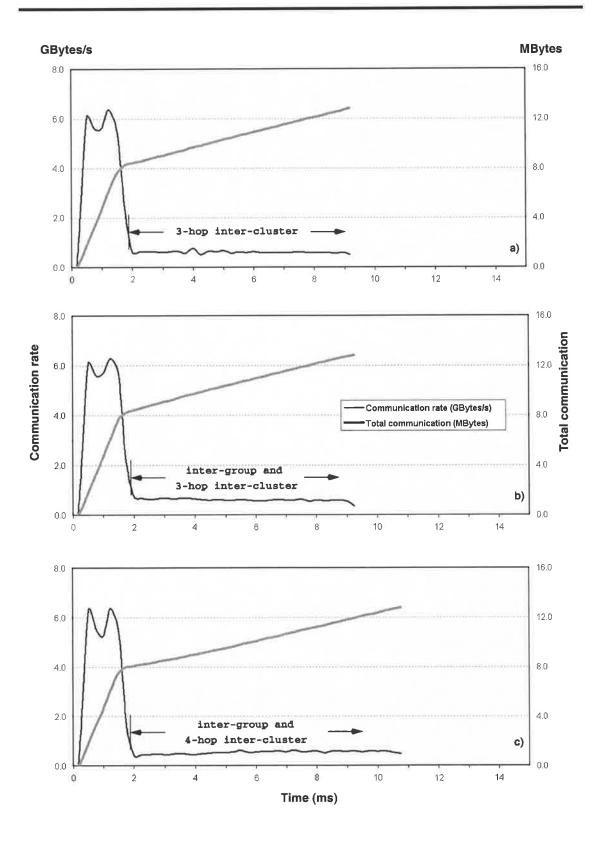

| Figure 7.11 | Mixed message types for improved network                                 | 157 |

| Figure 8.1  | Mesh structure                                                           | 170 |

| Figure 8.2  | Increasing port count of multiport memory                                | 171 |

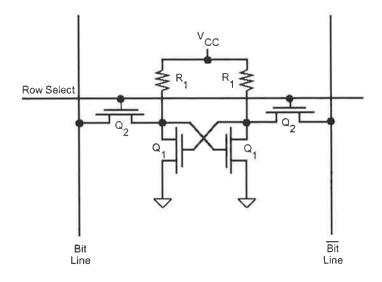

| Figure A.1  | Typical four-transistor SRAM cell                                        | 173 |

| Figure A.2  | The structure of 16x1 bits RAM                                           | 174 |

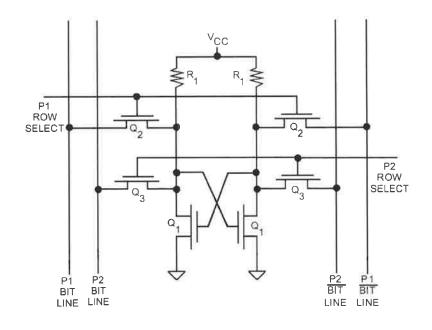

| Figure A.3  | Dual-port SRAM cell                                                      | 176 |

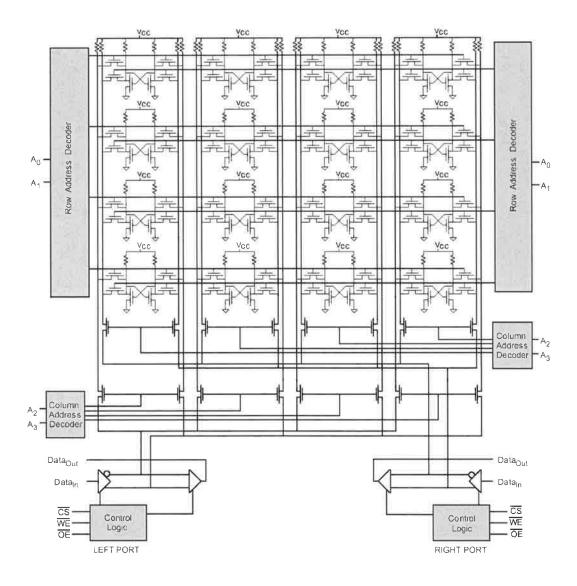

| Figure A.4  | Structure of 16-bit dual-port memory                                     | 177 |

| Figure A.5  | Busy logic for dual-port memory                                          | 178 |

| Figure A.6  | Modified arbitration latch                                               | 180 |

| Figure A.7  | Interrupt logic for signalling                                           | 181 |

| Figure A.8  | Architecture of multiport memory                                         | 183 |

| Figure A.9  | Semaphore logic for multiport memory                                     | 186 |

| Figure A.10 | Interrupt logic for multiport memory                                     | 188 |

| Figure A.11 | Interrupt latch design                                                   | 189 |

### **List of Tables**

| Table 5.1 | Algorithm for lock with BUSY    | 85 |

|-----------|---------------------------------|----|

| Table 5.2 | Algorithm for fast lock         | 88 |

| Table 5.3 | Basic communication protocol    | 91 |

| Table 5.4 | Protocol for dynamic allocation | 95 |

### **List of Publications**

- [1] Asgari N and Burgess N, "Multiport Memory for High-Speed Interprocessor Communication in MultiCom", the International Journal of Science and Technology, Scientia Iranica, Sharif University of Technology, Tehran, Iran, vol. 8, no. 4, pages 322-31, October 2001.

- [2] Asgari N and Burgess N, "The Structure and Design of MultiCom, a

Small Multiprocessor with Multiport Memory Based

Communication", in Proceedings of the Third Australasian Computer

Architecture Conference (ACAC'98), Perth, Australia, pages 15-24,

Springer-Verlag, February 1998.

- [3] Asgari N and Burgess N, "Memory Management and Dynamic Allocation of MultiCom", in Proceedings of the Forth Annual International CSI Computer Conference (CSICC'98), Tehran, Iran, pages 72-81, January 1999.

- [4] Asgari N and Burgess N, "Interprocessor Communication in Tree Structured Multiprocessors Using Multiport Memory", in Proceedings of the Forth Australasian Computer Architecture Conference (ACAC'99), Auckland, NZ, pages 161-72, Springer-Verlag, January 1999.

Multiport Memory as a Medium for Interprocessor Communication in Multiprocessors

### Introduction

CHAPTER 1

his thesis makes the case for the use of multiport memories for interprocessor communication in multiprocessors. In this introductory chapter, the and the motivation for background the research undertaken are presented briefly and the objective and scope of the study are outlined. In addition, the contributions made by the study are put forward. Finally, the structure of the thesis including a short explanation of the contents of each chapter is presented.

1

#### **1** Background and motivation

Interprocessor communication is one of the major activities in a multiprocessor system. There is a frequent demand for interaction and exchange of data among nodes and a high communication bandwidth is required. Interprocessor communication can be regarded as the dominant component affecting performance in multiprocessors. An efficient communication scheme requires high bandwidth and reliability with minimal cost and software/hardware overheads.

Two major communication structures for multiprocessors are shared memory and message passing. In shared memory systems, processors have access to a common memory and communication is performed implicitly by memory load and store instructions. One processor can write a message in the shared memory and other nodes can receive the message by reading it. Sharing a conventional single-port memory among nodes using a bus is one method to realize this concept. In this method, the nodes need to take turn in using the shared memory and only one node can use it at a time. Because of the limited bus bandwidth, this method is only useful for small number of processors. Examples of this structure can be found in [Tabak 90], [Culler+98], and [Patterson+98].

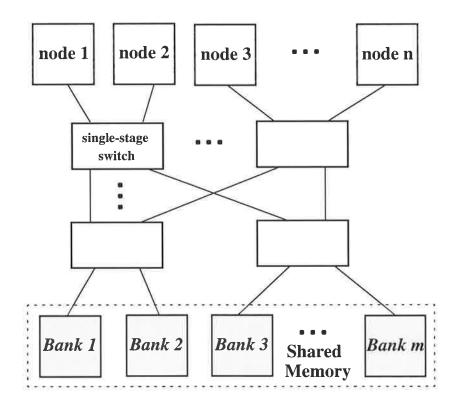

In an interleaved memory structure, various blocks of memory are shared among several nodes using different techniques. Nodes can access different memory banks simultaneously; however, only one access per bank is allowed. Multiple bus or crossbar switch can provide non-blocking connection of nodes to memory banks at high cost. Multistage networks reduce the cost, but full connection of processors to the memory banks may not be possible because of the blocking nature of the network. Memory interleaving is useful for medium-size systems and it has been the basis of many multiprocessors. Several examples can be found in [Tabak 90] and [Gajski+ 83].

In message passing systems, the nodes are interconnected by a communication network. Nodes communicate with each other by explicit send and receive commands. A low to medium number of nodes can be interconnected using topologies such as ring or mesh. For larger systems, hypercube is a better topology and some massively parallel processors have used this structure to interconnect up to  $2^{16}$  nodes [Hennessy+ 94]. In

these topologies communication is performed through serial links. The required wiring for connecting nodes in a network of this size is a challenging task. In addition, the slow nature of a serial link that sends data bit by bit is a limiting factor to achieve high communication rates.

Message passing through dedicated parallel links has been also investigated by researchers. For example, [Tuazon +85] suggested the use of first-in, first-out (FIFO) buffers between two nodes. The transmitting node had to write the message into the FIFO, and the receiving node could retrieve it from there. Similarly, [Su+ 92] proposed the use of FIFO RAMs to act as a communication buffers between nodes.

Developments in dual-port memory structure have initiated new methods for interprocessor communication. Dual-port memories allow two devices to have independent and simultaneous access to the memory cells. The nodes connected to a dual-port memory can communicate in both directions using two separate ports. As the overhead of bus is eliminated, higher communication rate can be achieved. Several structures have been proposed for interconnecting a limited number of nodes in [Jagadish+ 89], [Khan+ 94], and [Campbell+ 96]. With only two ports to access the memory, this approach is restricted to small systems.

Multiport memory offers a better structure for interprocessor communication. Several nodes can share a multiport memory using independent ports and they can communicate directly by writing and reading the shared memory concurrently. This structure is much simpler than other shared memory structures such as multiple bus or multistage networks and it does not have the overhead and the delay associated with these structures. The limiting factor is the small size and low number of ports on multiport memories. This restriction makes the design of communication structures for large systems very challenging. The structure proposed in this study is based on limited number of ports, and the shared memory created by multiport memory is used as a link for message passing. Unlike other shared memory systems, the shared memory in this structure is exclusively used for communication purpose and as explained later, a small memory size is adequate for this purpose.

As explained in Chapter 3, the concept of using multiport memory for interprocessor communication has not been deeply explored by researchers and only very few structures for basic communication have been proposed in [Handy 90] and [Varshneya+94]. No evaluation of the proposed structures has been performed. Hence, this is an open research area and the challenging nature of it, together with the expected benefits and outcomes are some of the incentives to undertake this research.

#### 2 Objectives and scope of the study

The main objective of this study is to demonstrate that interprocessor communication in multiprocessors can be performed efficiently through multiport memories. Suitable structures can be designed in which multiport memory with limited port count and capacity can be used as a link for message passing.

This study covers the following:

- Designing a basic structure for using multiport memory for interprocessor communication with a limited number of ports and capacity

- Developing strategies for the management of multiport memory

- Developing the required communication protocols

- Designing structures to connect a large number of nodes in a network

- Developing support facilities for multiport memories

#### **3** Contributions

This study explores the possibility of using multiport memory for interprocessor communication. Contributions claimed by the author are the following:

- Communication structure

- Multiport memory management

- Communication protocols

- Support circuits for multiport memory

Each one will be discussed briefly in the following sections.

#### 3.1 Communication structure

The concept of using dual-port memory for interprocessor communication has been explored by some researchers and successful outcomes have been reported. However, the use of multiport memory for this purpose has not been examined in depth and apart from a couple of proposed structures as presented in Chapter 3, there has been no significant work in this area. Furthermore, no work has been carried out to evaluate the proposed structures.

This study proposes a novel structure for interprocessor communication using multiport memory and supports the proposed structure by evaluating it with a hardware prototype and a simulation model. The hardware prototype tests the functionality and effectiveness of the structure under real conditions, and the simulator provides further in-depth tests of the expanded structure for conditions that cannot be tested easily on real systems. The hardware prototype was also used to calibrate the simulator to produce more reliable results when expanded. After several revisions of the structure based on the results obtained from the simulation model, the final structure presented in Chapter 7 was devised for medium to large-scale systems.

Compared to a system using dual-port memories, this structure offers a considerable increase in performance, and a remarkable decrease in the cost of the system as presented in Chapter 5. In addition, it enjoys a much simpler design and reduced number of links. It also shows much better results compared to bus-based systems or systems using serial links.

#### **3.2 Multiport memory management**

The proposed structure relies on conflict-free flow of data through multiport memory. As each node is connected to a multiport memory through an individual port, the possibility of a conflict between nodes is very high. The memory management of the multiport memory requires hardware support facilities or software-driven mechanisms for removing the conflicts or avoiding them. Because of the lack of hardware supports on multiport memories, the memory management developed in this study was based on software methods. In particular, two newly devised algorithms for implementing a lock mechanism for multiport memory were successfully implemented and tested on the hardware model in Chapter 5. These locks were used in dynamic allocation of the memory buffers to the requesting nodes.

#### **3.3 Communication protocols**

In order to effectively control the communications in the hardware prototype, a basic communication protocol was developed and tested on MultiCom in Chapter 5. The simulator designed in Chapter 6 was used to evaluate the scaling of the communication structure in several stages and the communication protocol was gradually modified to support the requirements of the expanded system. More improvements were applied to the communication protocol to meet the requirements of the improved communication structure in Chapter 7.

#### **3.4 Support circuits for multiport memory**

As discussed in Chapter 5, support circuits such as semaphore logic facilitate the use of dual-port memories. If similar facilities are not available on multiport memories, software approaches need to be developed for memory management and overhead will increase. This reduces the usefulness of multiport memory in a system design. In the Appendix, several new support circuits for multiport memories are proposed and designed. In particular, the new circuit designed for multiport semaphore logic considerably simplifies the management of multiport memory and makes the use of this type of memory more convenient. The designed circuits are practical and have been tested by hardware design tools.

#### **4** Thesis structure

This thesis is divided into eight chapters and one Appendix. Each chapter is discussed very briefly in the subsequent sections.

#### 4.1 Background

Chapter 1 presents a brief introduction and the motivation for the research undertaken. The objective and scope of the study are discussed, the contributions claimed by the author are presented, and the structure of the thesis is explained.

#### 4.2 Interprocessor communication

Chapter 2 presents the literature review for interprocessor communication. Shared memory and message passing as two major communication architectures in multiprocessors are explained and different approaches for designing each method are presented. For shared memory, single-bus and interleaved memories are discussed and the use of multiple bus, crossbar switch or multistage networks for connecting several nodes to memory banks is illustrated. For message passing systems, the use of serial links in topologies such as ring, mesh or hypercube is discussed and other structures that can create a dynamic link between two nodes on demand are reviewed. In addition, the use of parallel links for message passing is explained and generating such links using FIFOs or dual-port memory is discussed.

#### **4.3** Multiport memory for interprocessor communication

Chapter 3 describes the research proposal for this study. In the literature review presented at the beginning of this chapter, the achievements in multiport memory cell design are explored and some of the applications of multiport memories in system design are reviewed. Then, a structure for interprocessor communication using multiport memories is proposed and the expansion of the structure to cover more nodes in a network is presented. The proposed structure is based on multiport memories with limited number of ports and small capacity in which shared memory is used as a link for message passing.

#### 4.4 Hardware model

Chapter 4 discusses the structure and implementation of MultiCom, a small multiprocessor designed as a hardware prototype to verify the efficiency of the proposed communication scheme on small scale. The node processors and the 4-port

memory used in this design are explained and a basic memory management method called static allocation is introduced. Finally, the performance of this system is compared to serial systems.

#### 4.5 Memory management

Chapter 5 introduces dynamic allocation as an advanced memory management scheme and discusses the required communication protocols. Dynamic allocation can provide a better memory utilization, but requires a sophisticated lock mechanism to eliminate shared memory conflicts. Two new software locks devised for the control of multiport memory are explained and the efficiency of the communication in MultiCom is measured and compared with other methods.

#### 4.6 Simulation model

Chapter 6 presents the design of a simulation model for the evaluation of larger systems. First, a model for MultiCom is generated and its performance is matched to that of MultiCom. Then, the simulation model is expanded to include more nodes in a cluster and the performance of the system is evaluated. The expansion of the model to encompass more clusters in a network is also explained and the communication bottleneck detected by the simulation model is discussed.

#### 4.7 Improved communication structure

Chapter 7 describes the modifications required for the communication structure. Based on the results obtained from the simulation model, a modified structure for nodes connected in a cluster is presented and an improved structure for connecting several nodes in a network is explained. Several issues on scaling the communication scheme are also discussed.

#### 4.8 Further directions

Chapter 8 is the conclusion. The steps undertaken in designing, evaluating, and improving the structure are described and the achievements are discussed. In addition,

several possibilities to improve the structure and further directions in pursuing this study are presented.

#### 4.9 Structure of multiport memory

The Appendix presents the evolution of single-port memory cells to dual-port and multiport memory cells. The control logic used on dual-port memory chips is explained and several issues in the design of multiport memory chips are discussed. In addition, new circuits for the control of multiport memory are proposed and designed.

#### **CHAPTER 2**

### Interprocessor Communication

nterprocessor communication in multiprocessors is a very important task and requires a high bandwidth. In the literature review presented here, first, shared memory and message passing as two major communication structures for multiprocessors are explained and different methods to realize each method are presented. In the shared memory structure, nodes can communicate with memory load and store instructions and different techniques such as single bus or interleaved memory can be used to create it. In message passing, nodes communicate with explicit send and receive commands using an interconnection network, which is generally based on serial links and can be organized using different topologies. Next, the use of dualport memory as a communication medium between two nodes is discussed and different communication structures based on dual-port memories are explored. Finally, shared memory using a multiport memory is introduced and some of the unresolved issues in designing large-scale multiport memories are presented.

#### **1** Introduction

Multiprocessors enhance the capability and performance of computer systems by using parallelism. Several interconnected processors can process different parts of a workload in parallel and finish it faster. Workload sharing demands close cooperation and frequent exchange of data between processors. Hence, interprocessor communication is a very important task in multiprocessors. In [Almasi+ 89], a parallel computer is defined as "a collection of processing elements that communicate and cooperate to solve large problems fast". In [Culler+ 98], parallel architecture is viewed as "the extension of conventional computer architecture to address issues of communication and cooperation among processing elements". Both of these definitions highlight the importance of communication in multiprocessors. For a high performance multiprocessor, the communication structure should provide a high bandwidth.

The communication architecture of the majority of multiprocessors falls within the following categories:

- · single address space or shared-memory

- message passing

In shared-memory architectures, processors share a single memory address space and communicate through the shared memory. In message passing systems, processors exchange data and other information by sending and receiving messages to each other. Both are discussed briefly in the subsequent sections.

#### 2 Shared memory

This class of multiprocessors uses a single memory address space that is shared among processors. Processors still can have private or local memories, but part of their memory space is mapped to a common physical memory that is accessible by all processors. Communication is performed implicitly through shared memory using conventional load and store instructions. Shared memory can be implemented in many ways and two popular methods for implementing it using a single bus and interleaved memory are discussed here.

#### 2.1 Shared memory with a single bus

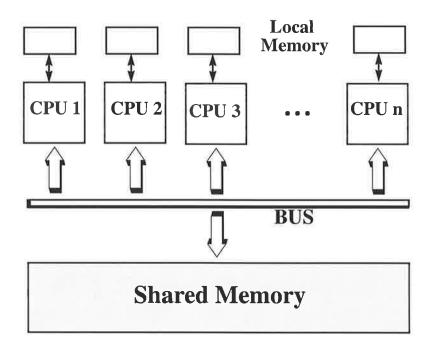

In this method, a conventional single-port memory is shared among several processors by a single bus, which has a fixed bandwidth. Implementing this bus is straightforward and processors can be added to the bus or removed from it if required, although the bus speed will be limited if the bus is long and/or many devices are connected to it. Because of the nature of the shared bus, only one request for the memory can be handled at a time and other requests have to wait for their turn. A control circuit such as arbitration logic is required to resolve simultaneous requests to memory. Under heavy bus demand, the limited bandwidth of the bus can create a bus bottleneck and consequently, this structure is only applicable when the number of processors is relatively low. The maximum number of processors on a bus depends on the bus bandwidth and the traffic per processor. Figure 2.1 illustrates the overall structure of a single-bus shared memory.

#### Figure 2.1 Simple shared memory

A conventional single-port memory can be used as a shared memory by using a bus. Only one request on the shared memory can be processed at any time. As a consequence of working in parallel, processors frequently work on shared data and need to coordinate their access to shared variables. As only one processor should be able to modify a shared variable, synchronization mechanisms such as locks or semaphores should be implemented to avoid memory conflicts. Semaphores will be discussed in detail in Chapter 5.

Shared memory structure has a long history, dating at least to precursors of mainframes in the early 1960s, and today it has a role in almost every segment of the computer industry. An example of earlier shared memory systems is IBM System 370. Supports for multiprocessor configurations including atomic memory operations and interprocessor interrupts were the key extensions in the evolution of the 360 architecture to System 370 [Culler+ 98].

Commercial examples of single-bus architecture are ELEXSI System from ELEXSI Corporation which features up to 12 processors connected to a single bus system called "Gigabus" [Tabak 90], and Compaq ProLiant 5000 from Compaq Corporation connecting four Pentium Pro processors [Patterson+ 98].

#### 2.2 Interleaved shared memory

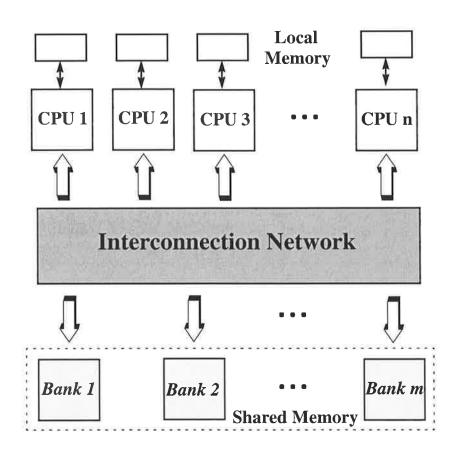

Memory interleaving is a method used for allowing several concurrent accesses to memory. In this method, the memory is divided into blocks or banks and an interconnection network is used to connect memory banks to the processors. Several processors can access different banks simultaneously; however, only one connection per bank is possible at a time. If more than one access to a particular bank is requested, only one of them can proceed while the others have to wait. Figure 2.2 demonstrates an interleaved memory structure.

Interconnection networks can be implemented using multiple busses, crossbar switches, or multistage networks. Each one will be discussed briefly.

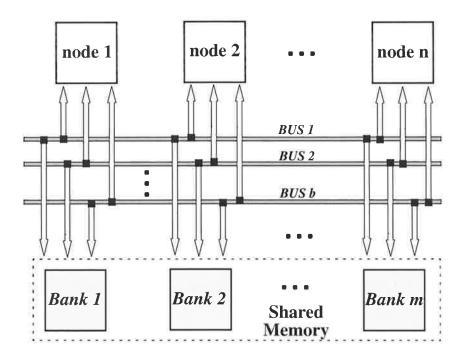

#### 2.2.1 Multiple-bus shared memory

In multiple-bus structures, processors and memory banks are connected to all of the available buses as shown in Figure 2.3. There are several redundant paths from each

#### Figure 2.2 Interleaved memory

The shared memory is composed of several memory banks and they are connected to different processors using an interconnection network.

processor to a memory module. Each processor can use any of the available buses to access a memory bank. Each bus can be used with only one processor at a time to access a memory bank, but several processors can access different banks simultaneously using separate buses. The cost and complexity of multiple-bus is very high. In addition, a complex bus arbiter is required to control the bus traffic. [Mudge+ 87] analyses multiple-bus structures in detail.

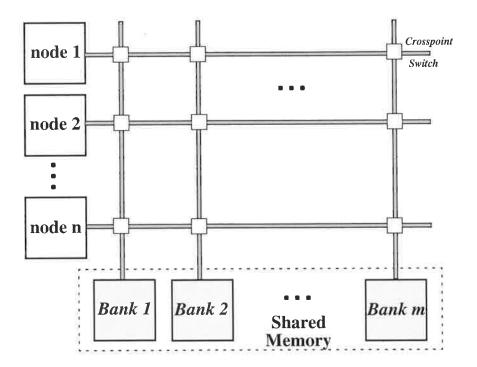

#### 2.2.2 Crossbar switch

A crossbar switch can also provide full connection of memory banks and processors. As shown in Figure 2.4, in a matrix of switches, processors are connected to the rows and memory banks to the columns. Crosspoint switches are placed in the intersection of

#### Figure 2.3 Multiple-bus shared memory

Processors and memory banks are connected to all buses. Each bank can be accessed using any bus. There are several redundant paths for each connection.

rows and columns and they can route each processor to a memory module. Crossbar switches scale well, but their cost is also high. For example, for N processors and N memory modules,  $N^2$  crosspoint switches are required. Moreover, for accessing memory bits in parallel, each bit should be routed by a separate switch. A crossbar switch is a nonblocking network and a connection between a processor and a memory module does not block the access of other processors to other memory modules. The structure in Figure 2.4 can be regarded as a multiple-bus system in which processors are connected to all buses, but memory banks are connected to only one bus. Hence, there is only one path from any processor to any memory bank.

An example of a commercial system using crossbar switches is IP-1 from International Parallel Machines Incorporation in which eight 64-bit processors were connected to 8 memory modules through an 8x8 crossbar switch. The Alliant System from Alliant Computer Systems Corporation also used a crossbar switch in its structure [Tabak 90].

#### Figure 2.4 Crossbar switch

Each memory bank is connected to a column line. Nodes can be routed to a memory bank by activating the appropriate crosspoint switch.

#### 2.2.3 Multistage network

A multistage network can reduce the cost of a switching network to  $(N/2) \log_2 N$ . As shown in Figure 2.5, instead of directly routing a processor to a memory module, several single-stage switches are activated in series to make the connections. Many structures for the design of multistage networks have been proposed and investigated in the literature. Examples are the omega, banyan, baseline, and delta networks. These are blocking networks and an existing connection may result in conflicts in the use of network and may block other connections. [Feng 81] presents a survey of interconnection networks in detail.

The circuit required to build the interconnection network can be large, especially if the number of nodes and memory blocks is high. In addition, as the circuit expands, the delay associated with it increases.

#### Figure 2.5 Multistage network

The nodes are connected to different memory banks using a multistage network. This structure is a blocking network. For example, routing node 1 to bank 1, and node 2 to bank 2 at the same time is not possible.

An example of a research machine using multistage networks is the "CEDAR" a largescale multiprocessor built in University of Illinois. It used a special switching network called "Global Network" which provided redundant paths between processors and memory modules for conflict avoidance and fault tolerance. It was designed to scale up to 1024 processors [Gajski+ 83]. A commercial example of multistage network is the BBN Butterfly from the BBN Advanced Computers, which could scale up to 256 processors, and the shared memory was accessible by all processors through the system's logarithmic, packet-switched communication network, the "Butterfly Switch" [Tabak 90].

# **3** Message passing

In this class of communication structure for multiprocessors, several nodes each comprising a processor, an I/O system and private memory are interconnected by a network. Communication between nodes is performed with explicit send and receive commands. If a message is large, it is divided into several packets and each one is sent independently. After receiving all the packets, the receiver can reassemble the original message. Message passing is usually slower than shared memory, but it avoids memory contention problems and scales very well.

Two general mechanisms for message passing are packet switching and circuit switching. The packet switching method works in a store-and-forward manner, analogous to the mail service. Each node stores the received message and then forwards it to the next node. The minimum message latency depends on the number of hops and the message length. In the circuit switching mechanism, a path from source to destination is initially established and remains connected until the message is transmitted in full [Gaughan+ 93]. This method is similar to a telephone switching system.

Nodes of a message-passing system can be interconnected using several topologies as explained in the next section.

## **3.1** Network topologies

The straightforward way to interconnect a number of nodes is to create a fullyconnected network in which a dedicated communication link is used between any two nodes. The links are normally bidirectional and data can flow in either direction. Between the high cost/performance of this network and the low cost/performance of a bus, there are several other networks that constitute a wide range of trade-offs in cost/ performance. Network costs include the number of switches, the number of links on a switch to connect to the network, the width or the number of bits per link, and the length of the links on the physical machine [Patterson+ 98]. Network topologies can be grouped into static and dynamic categories, depending on the type of links used in the network. These are explained in the subsequent sections.

#### **3.1.1 Static topologies**

In a static topology, links between two processors are passive and dedicated buses cannot be reconfigured for direct connection to other processors [Feng 81]. Some of the topologies in this category are discussed below.

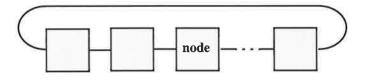

In a ring topology as shown in Figure 2.6, each node is connected to two adjacent nodes and several simultaneous transfers are possible. A message sent to a nonadjacent node will require extra hops to go through intermediate nodes. The maximum number of hops for N nodes is N/2. As the average message delay and message traffic density increase with the number of nodes on the ring, this topology is only useful for small systems.

Figure 2.6 Ring topology

In the ring topology, each node is connected to two adjacent nodes and the end nodes are connected together.

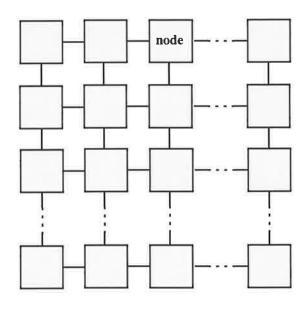

In a mesh or grid topology as illustrated in Figure 2.7, the nodes are arranged in a twodimensional grid and each node is connected to the adjacent nodes. A node will have a maximum of four direct links to adjacent neighbours. For N nodes, the communication of two nodes located on two opposite corners will take  $2(\sqrt{N} - 1)$  hops. This is 30 hops for N=256.

Nodes can be also arranged in a three-dimensional grid. In this topology, each node will be connected to a maximum of six adjacent nodes.

#### Figure 2.7 Mesh or grid topology

The nodes are arranged in a two-dimensional grid. Each node in the middle is connected to four adjacent nodes, but the corner nodes and boundary nodes are connected to two or three nodes respectively.

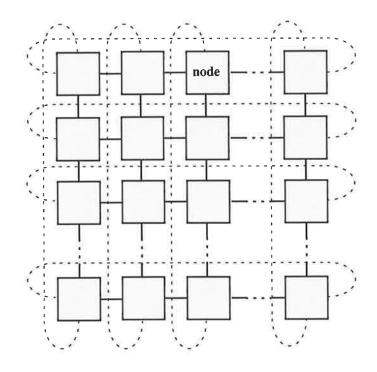

In a ring-mesh topology, a combination of ring and mesh is used. The corner and boundary nodes of a mesh structure are interconnected using several rings as shown in Figure 2.8. For N processors arranged in a ring-mesh array of  $\sqrt{N} \times \sqrt{N}$ , the longest path between any two processors requires  $\sqrt{N}$  hops. This is 16 hops for N=256.

A three-dimensional grid can be also converted to a ring-mesh topology by connecting the boundary nodes using several rings. This will reduce the number of maximum hops required in the network.

A network of Transputers is a good example of the ring-mesh topology. Transputers can be used as the main elements of a multiprocessor system and there are four serial ports on each chip [Inmos 88]. Several Transputers can be interconnected using this topology and the serial ports on each processor are fully utilized. A 4-cube topology as explained below is also suitable for a network of 16 Transputers.

#### Figure 2.8 Ring-mesh topology

A combination of ring and mesh is used in this topology. Each node is connected to four other nodes.

For a larger N, hypercube is a better topology where the number of links per node and the number of hops are optimized. For N=2<sup>n</sup> nodes, each node should have n=log<sub>2</sub>N links and the required hops to communicate from any node to another is the Hamming distance between the node numbers [Bhuyan+ 84]. The longest distance is  $log_2N$ , which is nine for N=2<sup>9</sup>=512. The number of total links is (N/2)log<sub>2</sub>N, which is 2304 links for 512 nodes. This hypercube is called an n-cube.

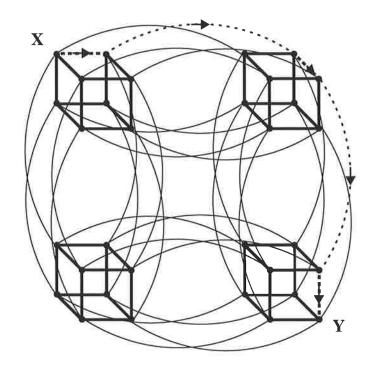

Figure 2.9 shows a 5-cube configuration with all of its 80 links. Communication between node X and node Y requires five hops. The arrows in the figure show one possible path for this communication. Figure 2.10 shows a 6-cube, and Figure 2.11 illustrates a 9-cube configuration. Only some of the links are shown in these figures.

The design of a microprocessor-based hypercube system is explained in [Hayes+ 86]. The Intel iPSC (personal supercomputer) and iPSC/2 are examples of commercial hypercube systems. They offer 5-cube, 6-cube, and 7-cube options. The iPSC uses

## Figure 2.9 32-node hypercube (5-cube) with all of its links

Each node in this hypercube is connected to its four neighbours through serial links. The dotted arrow shows one possible way of connecting node X to node Y.

#### Figure 2.10 64-node hypercube (6-cube)

In a 64-node hypercube, there is a 3-cube in each corner of a cube. Only some of the links are shown.

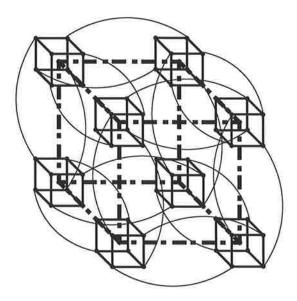

Figure 2.11 512 node hypercube (9-cube)

A 9-cube is composed of a cube with a 6-cube in each corner. Only some of the links are shown.

80286 processors with 80287 coprocessors and iPSC/2 is the 80386 version [Tabak 90]. Another example is the CM-2 supercomputer with  $2^{16}$  processors. It is a massively parallel machine from the Thinking Machines Corporation and uses a 12-cube configuration for its interprocessor communication. Each node of the hypercube is a cluster of  $2^4$ =16 processors. There are also other dedicated links for communication inside each cluster [Hennessy+ 94].

Other examples in static category are the star, tree, systolic array, and chordal ring topologies [Feng 81].

## 3.1.2 Dynamic topologies

In contrast to static topologies, the links in a dynamic topology are not fixed and can be reconfigured. This can be done by setting the network's active switching elements [Feng 81]. Hence, when required, a dynamic link can be established between two nodes for direct communication.

Dynamic links can be created using an interconnection network based on crossbar switches, multistage switches, or ATM (Asynchronous Transfer Mode) switches. The structure of an interconnection network using a crossbar switch is similar to the one shown in Figure 2.4 with the exception that the memory modules are replaced with nodes 1 to n. This implies that each node will have one input link and one output link connected to the network. Hence, a direct path can be created between any two nodes by setting the appropriate crosspoint switch. Similarly, by replacing the memory modules with nodes, the multistage switch shown in Figure 2.5 can route a path for the communication of two nodes. As stated earlier, this is a blocking network, but it costs less than a crossbar switch network.

Some of the static topologies shown in previous section can be constructed using dynamic links. For example, in the ring topology shown in Figure 2.12, each node is connected to the ring using a switch [Patterson+ 98]. The switch is capable of isolating the node from the ring, or connecting it the right or left side. With some restrictions, several communications can be performed simultaneously. For example, the two nodes on the right of Figure 2.12 can communicate with each other while the two nodes on the left are also communicating.

#### Figure 2.12 Ring topology with dynamic links

Each node is connected to the ring using a switch. Limited simultaneous communications are possible.

An example of a commercial computer using dynamic links is the CM-5, a supercomputer from the Thinking Machine Corporation, which is designed using an advanced structure called "fat-tree" for its interprocessor communication [Hennessy+94]. Another example is IBM SP-2, which is a scalable parallel machine constructed essentially out of complete RS6000 workstations. The interconnection network is a butterfly-like structure, constructed by cascading 8 x 8 crossbar switches [Culler+98].

## **3.2 Interconnection methods**

An interconnection network can be implemented using serial links or parallel links. Each one will be explained briefly in the subsequent sections.

#### 3.2.1 Serial links

Communication using serial links is a well-established method where the message is transmitted serially from one processor to another, one bit at a time. Serial communication can be performed point-to-point, or on a network using multistage switches. In the simplest form, the link is composed of a pair of wires that runs between two nodes. The major disadvantage of this link is its low data rate, which is the result of the serial nature of the communication that sends data bit by bit at usually low data rates. Its advantage is that it significantly reduces the number of wires used in the network. Another advantage is that as serial communication is normally performed using independent modules, the main processor is not heavily engaged in the communication and is free to perform other tasks while the communication is running in the background.

## 3.2.2 Parallel links

Parallel links are capable of transferring several bits of data at the same time. For a data transfer, the sender writes to the link and the receiver reads from the link. A simple parallel link can be created by connecting an I/O port of a node to that of another node. This method requires extensive handshaking between the nodes and each unit of data needs to be signalled and acknowledged before sending others. The data bus of a memory module can be also used as a parallel link for data transfer. [Tuazon +85] suggested the use of first-in, first-out (FIFO) buffers as parallel links between two

nodes. The transmitting node had to write the message into the FIFO, and the receiving node could retrieve it from there. Similarly, [Su+ 92] proposed the use of FIFO RAMs to act as communication buffers between nodes. [Culler+ 98] explains an early system in which eight nodes were connected in a 3-cube structure and there were two sets of FIFOs between two neighbours for sending and receiving. A total of 24 FIFOs were used in this structure. Because of the limited size of FIFOs, a message sent to a FIFO should be picked up by the receiver before sending another message.

The availability of dual-port memory in the second half of the 1980's provided a better solution than FIFOs because of its ability to work in both directions and many structures were proposed on this basis. As the discussion of dual-port memory is vital to the communication structure proposed in this thesis, it is covered in a separate section.

#### 3.2.3 Dual-port memory

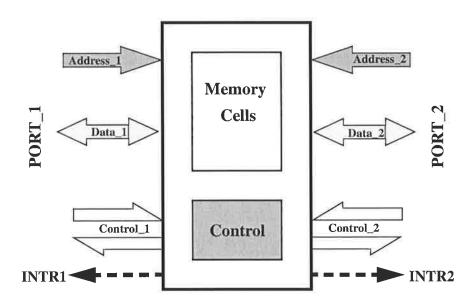

As shown in Figure 2.13, a true dual-port memory has two sets of address, data, and control lines. Each memory location can be accessed through either of the ports.

#### Figure 2.13 Dual-port memory

A dual-port memory has two sets of address, data, and control buses. The memory cells can be accessed from either port. The chip may contain signalling facilities between the ports, like an interrupt line that alerts one side when data has been written by the other. Simultaneous read and writes are allowed, provided that they are performed on different addresses. In order to achieve data integrity, two concurrent writes to a memory location should be prevented. Similar prevention methods should be applied to a concurrent read and write because this may produce changing data at the output of the read operation.

A typical dual-port memory has a size of 16 to 64 KBytes with the facility of preventing undesired operations, as well as a mechanism to send an interrupt from the processor connected to one of the ports to the processor connected to the other port. The interrupt mechanism works by simply writing to a specific memory location. [Cypress 96].

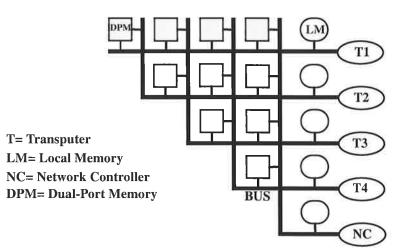

Dual-port memory can be used as a register file inside a processor where two sets of data are supplied to the ALU (arithmetic logic unit). By the use of simple latches at the ALU inputs, the output of the ALU could be written back to the register file [Elliot+ 89]. There are several other applications for dual-port memories such as digital video cameras, data acquisition systems, displaying data on a monitor, and communication between processors. The latter application is one of the major applications of the dual-port memories [Wyland 88] [Pryce 89]. There is a preliminary report on the use of dual-port memory for a cluster of four Transputers and a network controller in [Khan+ 93]. The next report from the same team discusses the detail of their design [Khan+ 94]. The architecture used in this design is illustrated in Figure 2.14, in which there is a separate

# Figure 2.14 Restricted Shared Memory (RSM) architecture for communication through dual-port memories

In this structure, a cluster of four Transputers and a network controller are interconnected using dual-port memories.

link through a dual-port memory from any node to the network controller or the other nodes. As seen in the figure, ten memory blocks were used in this architecture to interconnect four nodes and a network controller.

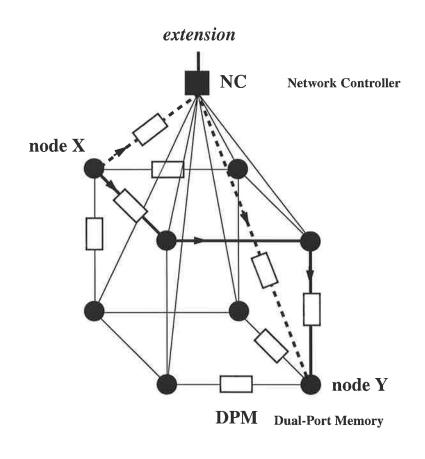

Another work is cited in [Jagadish+ 89], in which dual-port memories were used to interconnect eight nodes and a network controller. As shown in Figure 2.15, each node in this design is located in a corner of a cube and has a separate link to three of its neighbours as well as another link to a network controller. Only the dual-port memories associated with node X and node Y are shown in this figure. The total number of dual-port memory blocks required for this structure is 20. Even with this number of memory blocks, the link between some nodes, such as nodes X and Y, must be established through the other nodes or the network controller as shown by the arrows.

#### Figure 2.15 Using DPM to connect nodes in a cube

The nodes are located in the corners of a cube and there is a dual-port memory between any two nodes. A network controller can facilitate the communication between non-adjacent nodes. Only DPMs connected to nodes X and Y are shown. Arrows show two possible paths between X and Y.

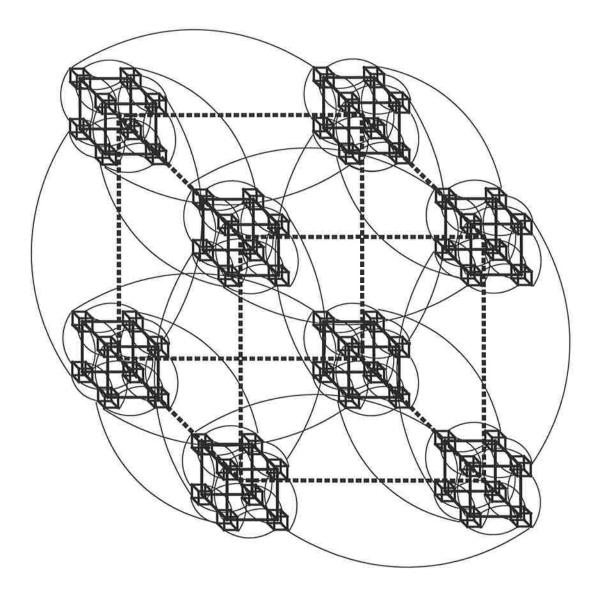

## **Figure 2.16 Extending the structure using DPMs to 64 nodes** In this structure, the network controllers of each cluster are interconnected using DPMs in a similar manner as nodes of a cluster. Only one DPM is shown, but the structure requires 180 DPMs

The authors have proposed that the structure could be extended to higher order cubes such as  $2^{6}$ =64 nodes (6-cube) as shown in Figure 2.16. The number of required memory blocks would be 180.

Both the structure presented in this work and the RSM discussed earlier combine the use of shared memory with message passing. In fact, similar to the structures using FIFOs described earlier, shared memory is used as a link between nodes for message passing.

The RSM architecture presented in [Khan+ 94] is similar to the structure used in [Jagadish+ 89]. As shown in Figure 2.17, the structure of Figure 2.14 can be viewed as a hypercube of order 2 in which four nodes are placed in corners of a square and each one shares a DPM with each adjacent node. In addition, the diagonal nodes are

Figure 2.17 Another view of RSM architecture

RSM structure can be viewed as a fully connected network for four nodes using DPMs. In addition, each node has a link to a network controller.

interconnected using other DPMs and each node has a link to a network controller. With the exception of the diagonal links, this structure is similar to the top part of the structure shown in Figure 2.15.

With the contributions from one of the authors of [Jagadish+ 89], the continuation of this research has been presented in [Campbell+ 96]. It was reported that a multiprocessor called COMPS (COmmon memory Message Passing System) was being developed in Curtin University of Technology in Perth, Australia and used a dual-port memory as the communication link between two nodes. A five-node prototype system was reported as being in its final stage and near completion. The results of this system will be reviewed in Chapter 4.

# **4** Convergence

Shared address space and message passing are two clearly distinct architectures. However, the evolution of hardware and software has gradually blurred the boundary and substantial convergence has taken place [Culler+ 98]. Some of these are explained below.

At the user level, most shared memory machines also support send/receive operations used in message passing through shared buffer storage. In addition, a shared virtual address space can be established on a message passing system. A group of processes can have a region of shared address space, but each process has access to its local pages. When a non-local page is addressed, a page fault occurs and the operating system initiates a message passing transaction to transfer the missing page and map it to the user address space [Culler+ 98].

As explained in the previous sections, shared memory can be used as links for message passing. Furthermore, with the advances in the design of scalable interconnect networks, several machines, which may be shared memory in their own right, are interconnected to operate as a parallel machine on individual large problems or as many individual machines on a multiprogramming load [Culler+ 98]. Such systems can utilize the advantages of both architectures.

The Stanford DASH multiprocessor (abbreviated for Directory Architecture for Shared Memory) was designed to investigate the scalability issues for shared-memory multiprocessors. As in message-passing machines, the main memory in DASH is distributed among the processing nodes and a scalable interconnection network is used to connect the nodes together. Unlike message-passing machines, however, the processing nodes share a single global address space. The DASH architecture thus combines the scalability of message-passing machines with the ease of programming associated with single address space machines [Lenoski+91].

The FLASH multiprocessor (abbreviated for Flexible Architecture for Shared Memory) also developed in Stanford supports distributed shared memory and message passing while minimizing both hardware and software overhead. Each node in FLASH contains a microprocessor, a portion of the machine's global memory, a port to the interconnection network, an I/O interface, and a custom node controller called "MAGIC". The MAGIC chip handles all communication both within the node and among the nodes, using hardwired data paths [Kuskin+94].

The underlying machine structures for message passing and shared address space have converged toward a common organization, represented by a collection of complete computers, expanded by a "communication assist" connecting each node to a scalable communication network. Thus, it is natural to consider supporting aspects of both in a common framework [Culler+ 98].

# 5 Shared memory using multiport memory

Multiport memories provide several ports for accessing the memory cells and each node of a multiprocessor can be connected to one of the available ports exclusively. All the nodes can simultaneously read from different memory locations. They can even read from the same memory location concurrently. In contrast to reads, simultaneous memory writes are only possible if different memory locations are used. If two or more concurrent writes to a memory cell are requested, only one of them should proceed.

The use of multiport memory as in Figure 2.18 can improve the performance of a shared-memory system significantly. This is because concurrent memory access is possible without the overhead of the bus system or the interconnection network. However, the main problem is that the available multiport memories have very few ports (maximum 4 ports at the time of conducting this research) and small capacities (2-4 KBytes for 4-ports) [ICmaster 99]. This small range is not sufficient to build a shared memory suitable for a relatively large number of nodes. There are several issues in the design of a large-scale multiport memory that need to be resolved before producing multiport memories with large capacity and more ports. Some of these issues are the complexity of the memory cells, the huge number of connections inside the chip, large pinout required by the chip, and a preventing mechanism for avoiding concurrent writes, or even concurrent read-write on the same memory cell.

The small port count and limited capacity of multiport memories make their use as a shared memory a challenging task. As explained in Chapter 3, this area has not been explored in depth, and only very few structures for interconnecting nodes in small systems have been proposed. Furthermore, no work has been reported previously in evaluating a communication scheme based on multiport memories and no attempt has been made to design the required memory management and associated communication protocol. Hence, the openness of the area, the challenging nature of it, and the expected advantages over other methods make it an excellent research area.

Figure 2.18 Multiport shared memory

Each node can be connected to one of the ports of an ideal multiport memory. They can communicate with each other through the shared memory.

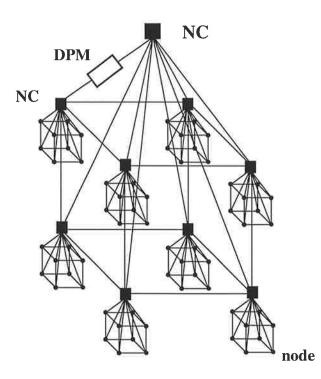

As multiport memory is the focus of this thesis, its use in interprocessor communication will be discussed in depth in Chapter 3. The proposed structure is based on multiport memories with limited size and port count. A small shared memory is created for interconnecting a small number of nodes. The memory is very small to be used as a normal shared memory, but it is large enough for use as a communication medium for message passing only. The scaling of the structure is performed by a network of multiport memories in which data is exchanged among the nodes using message passing. The structure of multiport memory cells and new circuits to resolve some of the issues in designing multiport memories are presented in the Appendix.

# **6** Conclusion

Interprocessor communication is a vital task for sharing data among the nodes in multiprocessors. Two major architectural techniques for sharing data in multiprocessors are shared memory and message passing. In shared memory systems nodes have access to a common memory using different techniques such as a single bus or interleaved memories. The communication among nodes is implicitly performed by load and store instructions.

A conventional single-port memory can serve as a shared memory using a single bus. This structure is only useful for a small number of nodes. Interleaved shared memory can provide higher memory bandwidth than a single-bus system and can be designed using multiple-bus, crossbar switch, or multistage networks.

In message passing systems, the nodes are connected by an interconnection network and they can share data by sending and receiving messages. Generally, there are explicit send and receive commands for communication. The interconnection network can use different topologies such as ring, mesh, or hypercube, and nodes can be connected using either conventional serial links or dedicated parallel links. In the latter case, a FIFO can be placed between two nodes and messages can be transferred in one direction by writing to and reading from it.

The advent of dual-port memory introduced new methods for interprocessor communication. A dual-port memory shared between two nodes can be used as a communication medium and nodes can communicate simultaneously in both directions using load and store instructions. Using appropriate structures, several nodes can be interconnected with dual-port memories.

Multiport memory provides more ports for concurrent access of memory. Ideally, it can be used as a communication medium for several nodes with very low overhead. However, the small number of ports and the limited capacity of the multiport memory make it less attractive. In the next chapter, a new structure for interprocessor communication based on multiport memory with limited port-count and small capacity will be presented in which shared memory is used as a link for message passing.

## **CHAPTER 3**

# Multiport Memory for Interprocessor Communication

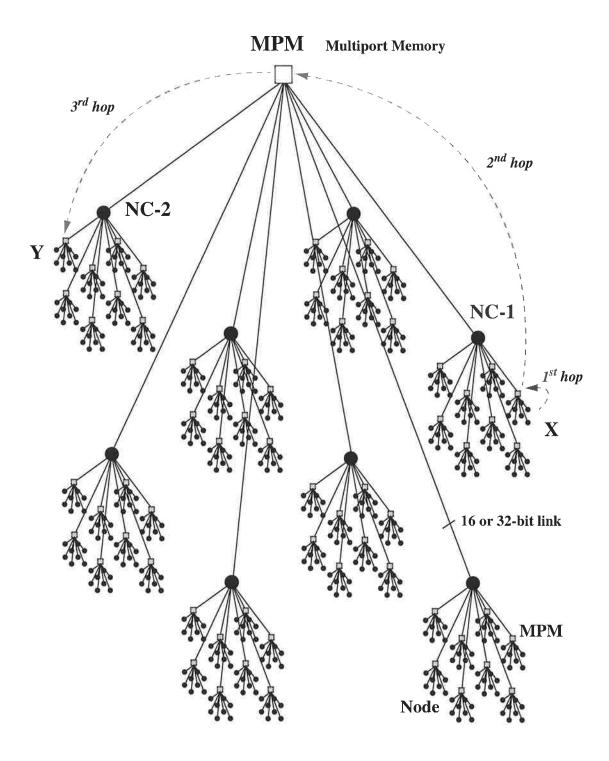

ultiport memories can facilitate the interprocessor communication in multiprocessors. Communication can be performed in parallel streams by accessing a multiport shared memory through independent ports. This method is capable of increasing the performance and reducing the size, cost, and the number of required components and interconnections. In this chapter, first, the advances in multiport cell design are explored and its applications in system design are presented. Then, an interprocessor communication scheme based on multiport memory is proposed in which shared memory is used as a link for message passing. For small systems, the nodes can communicate directly in a group structure. Groups can be connected in a cluster, and a network controller would handle the inter-group messages. For expanded systems, the network controllers of various clusters can be interconnected by sharing a multiport memory at the top of the hierarchy. Finally, several issues related to multiport memories are discussed.

35

# **1** Multiport memory: background and previous work

Multiport memory offers new communication methods for multiprocessors and can provide high-speed communication using parallel streams. In a small-scale system using this method, each node can use a separate port to access a multiport memory shared among the nodes. One node can write data into the shared memory from one port, and other nodes can read it from other ports. Nodes can communicate in parallel and achieve high performance, provided that they do not interfere with each other. This is achievable by proper memory management schemes. The limiting factor in scaling this structure is the limited number of ports and the small size of true multiport memories. Hence, special structures need to be designed for building larger systems.

A multiport memory cell is similar to a dual-port memory cell, but there are more than two ports to access the cell. The block diagram of a 4-port memory is shown in Figure 4.2 on page 57. The internal circuit and operation of multiport memory are explained in detail in the Appendix.