### **Architectures for Floating-Point Division**

Hooman Nikmehr

B.Sc. University of Tehran M.Eng.Sc. University of Tehran

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in the School of Electrical and Electronic Engineering The University of Adelaide Australia

Supervisors: Dr. Cheng-Chew Lim and Dr. Braden Phillips

August, 2005

Copyright ©2005 Hooman Nikmehr All Rights Reserved

# Contents

| Ał  | Abstract xv                   |         |                                   |  |   |   |      |

|-----|-------------------------------|---------|-----------------------------------|--|---|---|------|

| Sta | Statement of Originality xvii |         |                                   |  |   |   |      |

| Ac  | Acknowledgments xix           |         |                                   |  |   |   |      |

| Pu  | Publications xxi              |         |                                   |  |   |   |      |

| Li  | st of I                       | Princip | al Symbols                        |  |   | x | xiii |

| Li  | st of A                       | Abbrev  | iations                           |  |   | x | cvii |

| 1   | Intro                         | oductio | n                                 |  |   |   | 1    |

|     | 1.1                           | Motiv   | ation                             |  | • |   | 2    |

|     | 1.2                           | Overv   | iew                               |  | • |   | 2    |

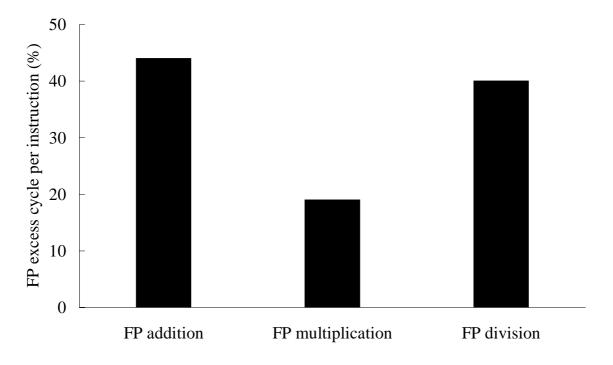

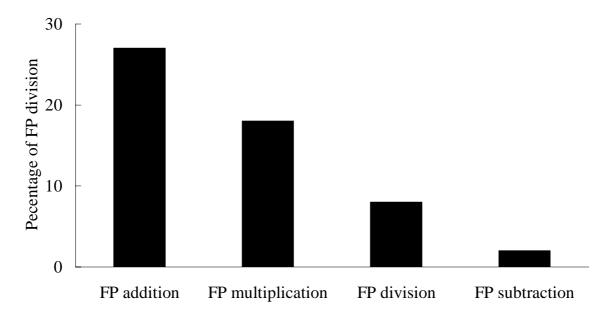

|     |                               | 1.2.1   | Importance of FP Division         |  | • |   | 3    |

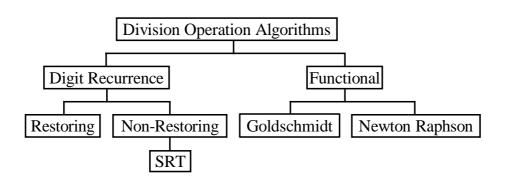

|     |                               | 1.2.2   | Division Algorithm Taxonomy       |  |   |   | 4    |

|     | 1.3                           | Resear  | rch Objectives                    |  |   | • | 6    |

|     | 1.4                           | Resear  | rch Contributions                 |  | • | • | 7    |

|     | 1.5                           | Thesis  | Organisation                      |  | • | • | 9    |

| 2   | Divi                          | sion A  | lgorithms                         |  |   |   | 11   |

|     | 2.1                           | Introd  | uction                            |  | • | • | 12   |

|     | 2.2                           | Functi  | onal Division Algorithms          |  | • | • | 12   |

|     |                               | 2.2.1   | Newton-Raphson                    |  |   | • | 12   |

|     |                               | 2.2.2   | Goldschmidt                       |  |   |   | 13   |

|     |                               | 2.2.3   | Newton-Raphson versus Goldschmidt |  | • |   | 14   |

|     |                               | 2.2.4   | Features                          |  | • | • | 14   |

|   | 2.3  | Digit l  | Recurrence Algorithms                                         | 15 |

|---|------|----------|---------------------------------------------------------------|----|

|   |      | 2.3.1    | Definitions and Notations                                     | 15 |

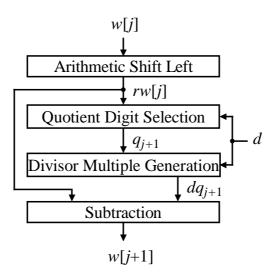

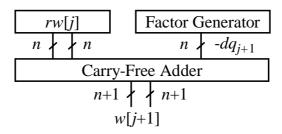

|   |      | 2.3.2    | Recurrence                                                    | 16 |

|   |      | 2.3.3    | Restoring Division                                            | 17 |

|   |      | 2.3.4    | Non-Restoring Division                                        | 19 |

|   |      | 2.3.5    | Redundant Digit Sets                                          | 20 |

|   |      | 2.3.6    | Radix-2 SRT Algorithm                                         | 21 |

|   |      | 2.3.7    | High-Radix SRT Algorithm                                      | 23 |

|   | 2.4  | Digit l  | Recurrence versus Functional                                  | 27 |

|   | 2.5  | Summ     | nary                                                          | 27 |

| 3 | SRT  | ' Divisi | on Algorithm Implementation                                   | 29 |

|   | 3.1  | Introd   | luction                                                       | 30 |

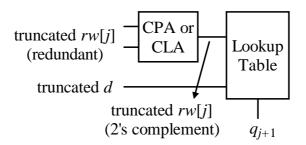

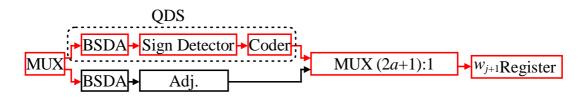

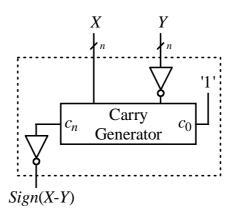

|   | 3.2  | QDS F    | Function                                                      | 30 |

|   |      | 3.2.1    | Introduction                                                  | 30 |

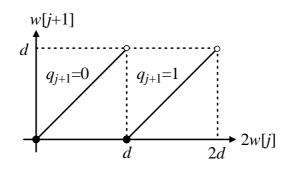

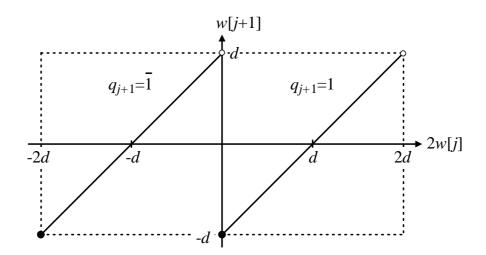

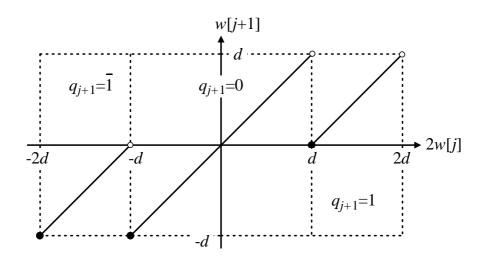

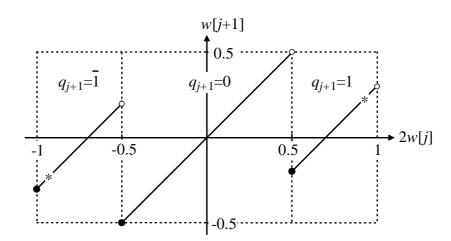

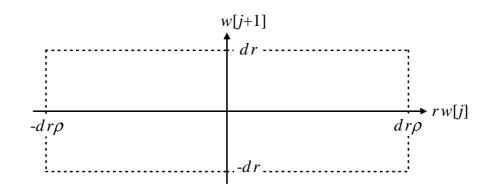

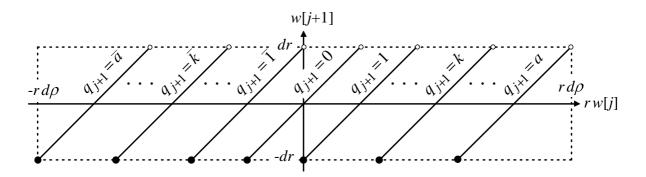

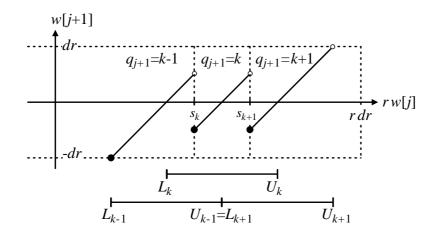

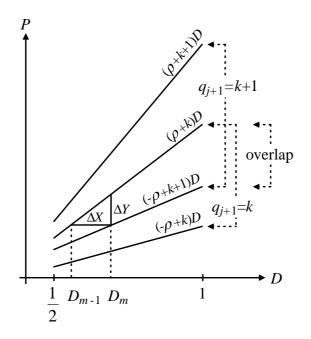

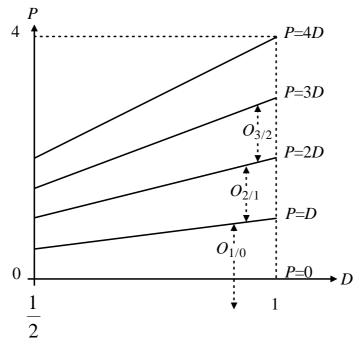

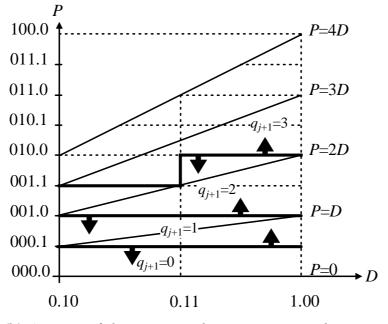

|   |      | 3.2.2    | PD Plot Method                                                | 31 |

|   |      | 3.2.3    | Selection Constants Method                                    | 38 |

|   | 3.3  | Divisi   | on Radix                                                      | 42 |

|   | 3.4  | Redur    | ndancy Factor                                                 | 43 |

|   | 3.5  | PR Re    | presentation                                                  | 44 |

|   | 3.6  | Quoti    | ent Conversion Method                                         | 45 |

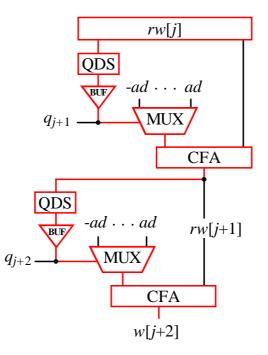

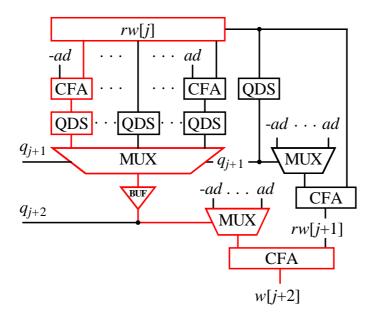

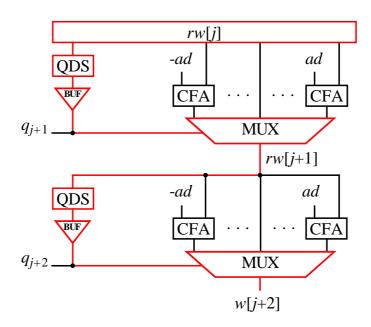

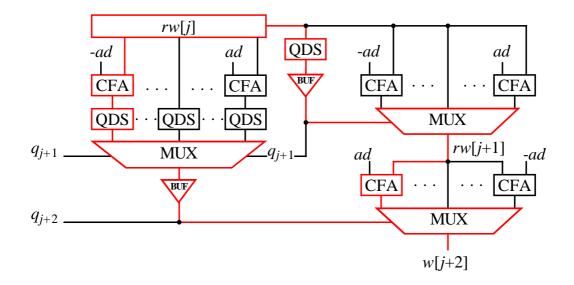

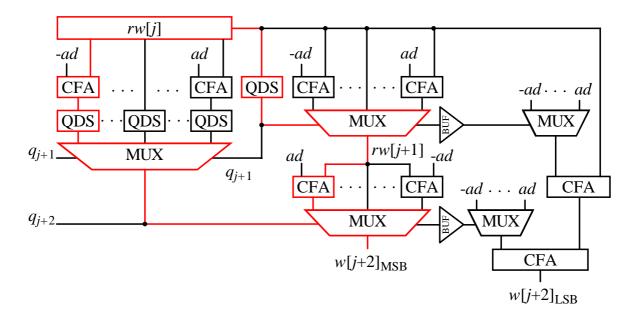

|   | 3.7  | Overla   | apping Iteration Components                                   | 46 |

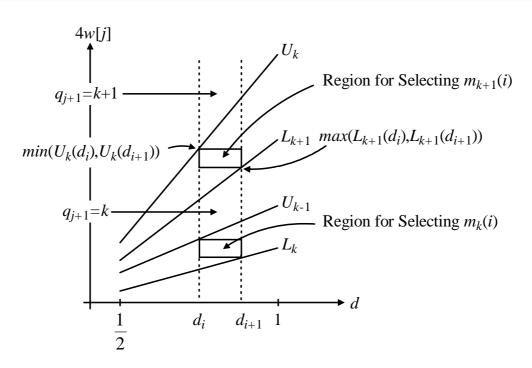

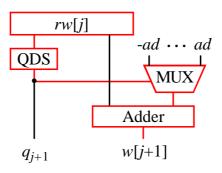

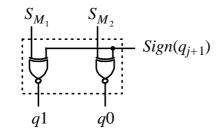

|   |      | 3.7.1    | Overlapped QDS Function                                       | 46 |

|   |      | 3.7.2    | Overlapped PR Formation                                       | 49 |

|   |      | 3.7.3    | Overlapped QDS Function and PR Formation                      | 50 |

|   |      | 3.7.4    | Hybrid Overlap                                                | 51 |

|   | 3.8  | Numb     | per Representation in the IEEE 754 Standard                   | 51 |

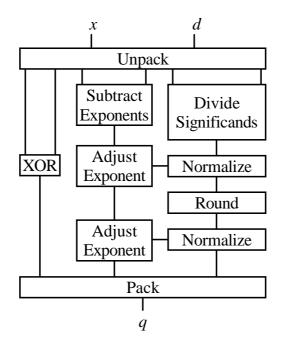

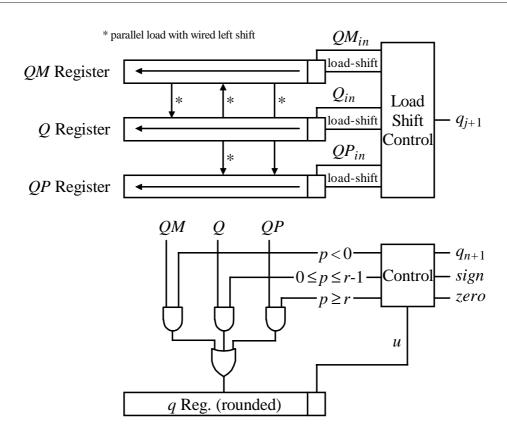

|   | 3.9  | FP Div   | vision Using the SRT Algorithm                                | 52 |

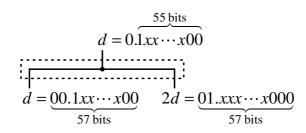

|   |      | 3.9.1    | Rounding and Post-Normalising                                 | 53 |

|   |      | 3.9.2    | Assumptions to Match SRT Division with the IEEE 754 Standard  | 56 |

|   | 3.10 | Summ     | nary                                                          | 57 |

| 4 | Con  | npariso  | n Multiples, a Different Approach to Quotient Digit Selection | 59 |

|   | 4.1  | Introd   | luction                                                       | 60 |

|   |      |          |                                                               |    |

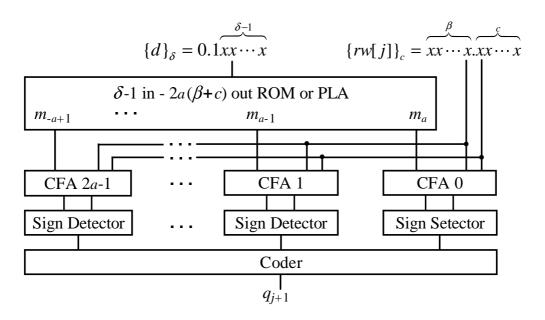

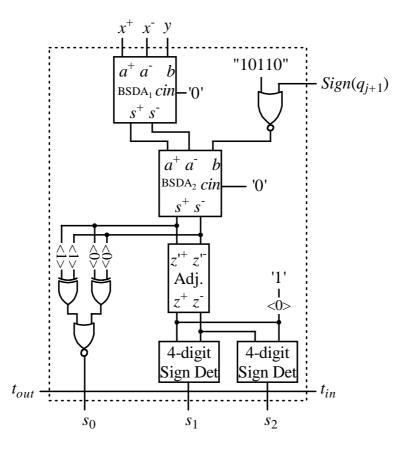

|   |            | 4.1.1                                                                         | Retimed Low Power Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61                                               |

|---|------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

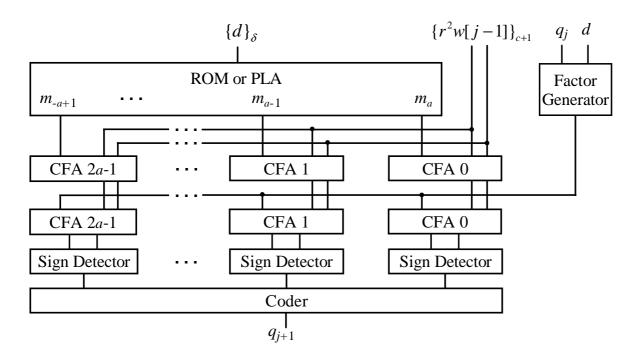

|   |            | 4.1.2                                                                         | Implementation Used in the ARM FP Macrocell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63                                               |

|   |            | 4.1.3                                                                         | Retimed Implementation of ARM Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65                                               |

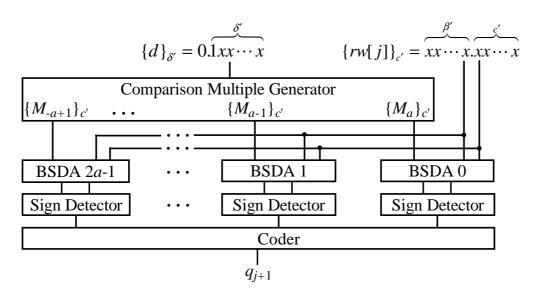

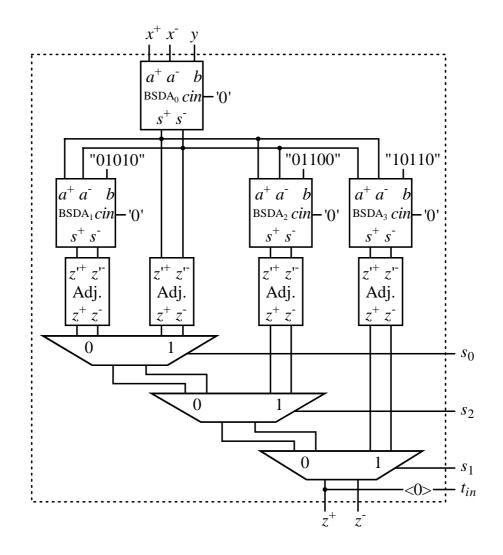

|   | 4.2        | Comp                                                                          | arison Multiples Based FP Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65                                               |

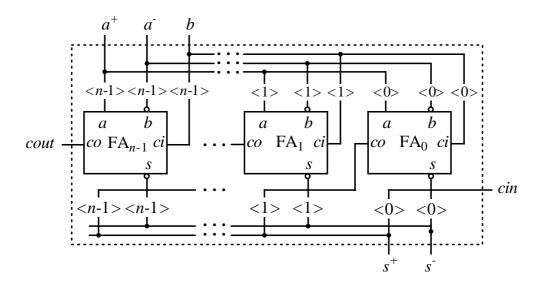

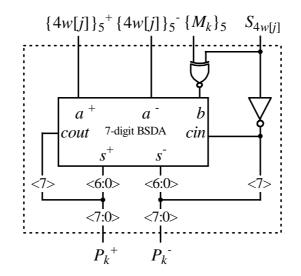

|   |            | 4.2.1                                                                         | PR Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                               |

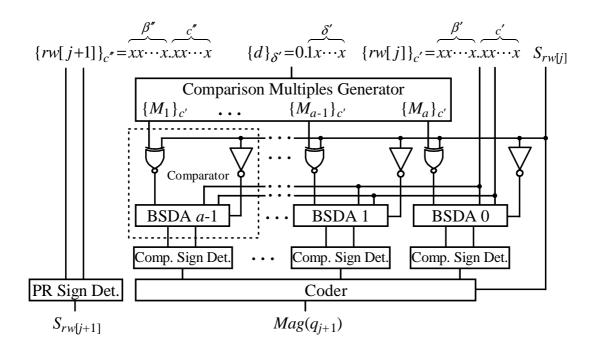

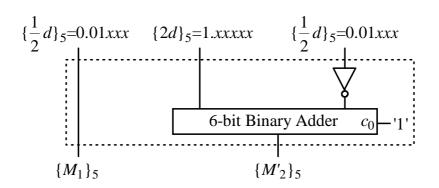

|   |            | 4.2.2                                                                         | Comparison Multiples Based QDS Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67                                               |

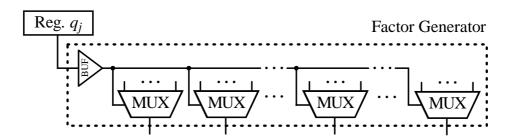

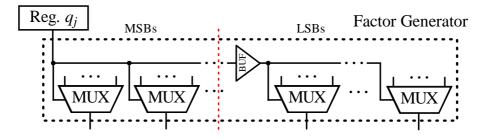

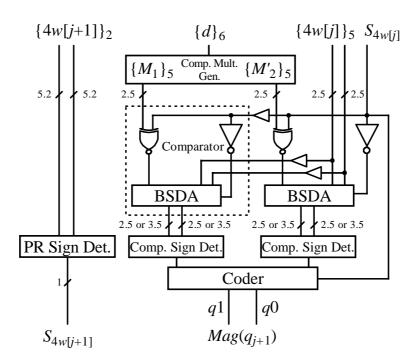

|   |            | 4.2.3                                                                         | QDS Function Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68                                               |

|   |            | 4.2.4                                                                         | QDS Function Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                                               |

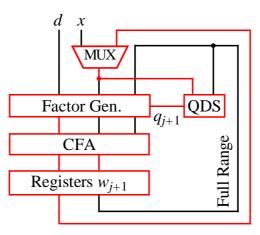

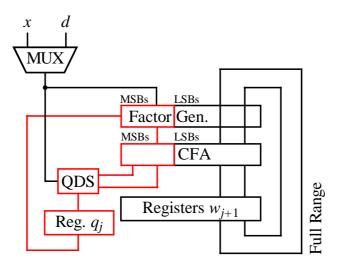

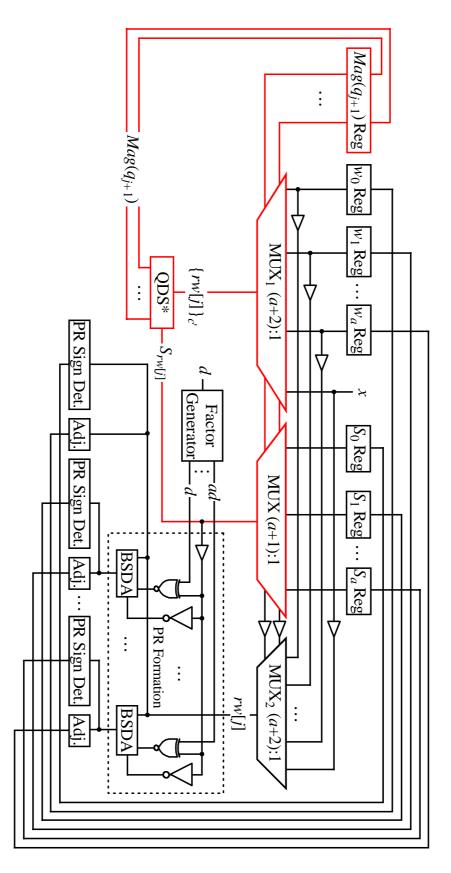

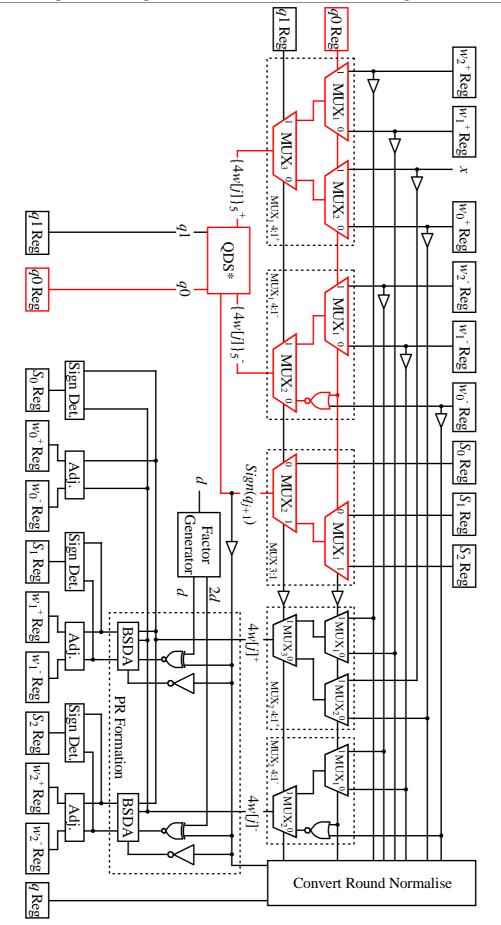

|   |            | 4.2.5                                                                         | FP Division Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72                                               |

|   |            | 4.2.6                                                                         | FP Division Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72                                               |

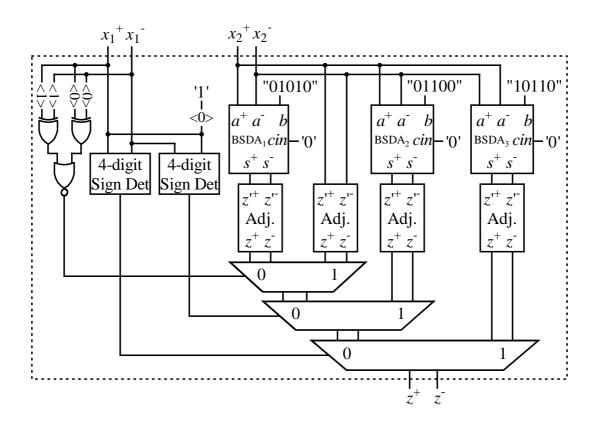

|   | 4.3        | FP Div                                                                        | vision Optimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                               |

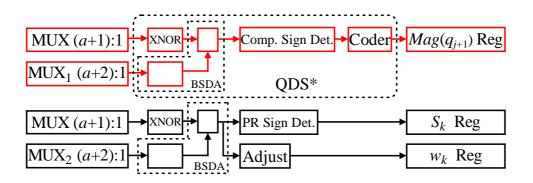

|   |            | 4.3.1                                                                         | QDS Function Optimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                               |

|   |            | 4.3.2                                                                         | Optimised QDS Function Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77                                               |

|   |            | 4.3.3                                                                         | Recurrence Optimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                               |

|   |            | 4.3.4                                                                         | Optimised Recurrence Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 78                                               |

|   | 4.4        | QDS F                                                                         | Function Operands Precisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80                                               |

|   |            | 4.4.1                                                                         | <i>e</i> ' and <i>c</i> '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80                                               |

|   |            | 4.4.2                                                                         | $e''$ and $c'' \dots $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82                                               |

|   | 4.5        | Summ                                                                          | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83                                               |

| 5 | Con        | npariso                                                                       | n Multiples Based Radix-4 and Radix-16 Floating-Point Dividers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85                                               |

|   | 5.1        | Introd                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |

|   |            | muou                                                                          | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86                                               |

|   | 5.2        |                                                                               | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86<br>86                                         |

|   | 5.2        |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |

|   | 5.2        | Radix                                                                         | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86                                               |

|   | 5.2        | Radix<br>5.2.1                                                                | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86<br>86                                         |

|   | 5.2        | Radix<br>5.2.1<br>5.2.2                                                       | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86<br>86<br>86                                   |

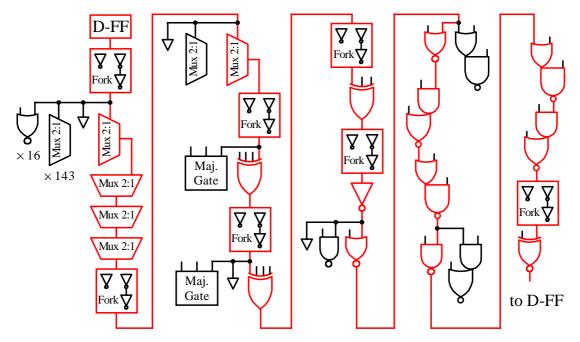

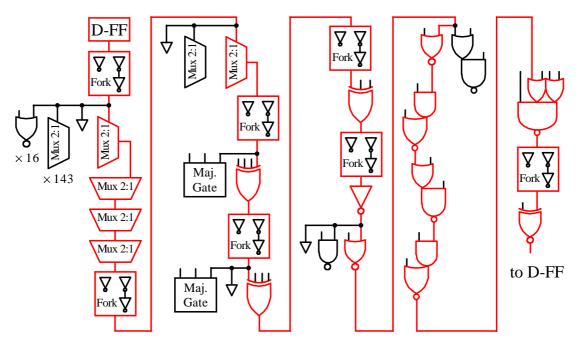

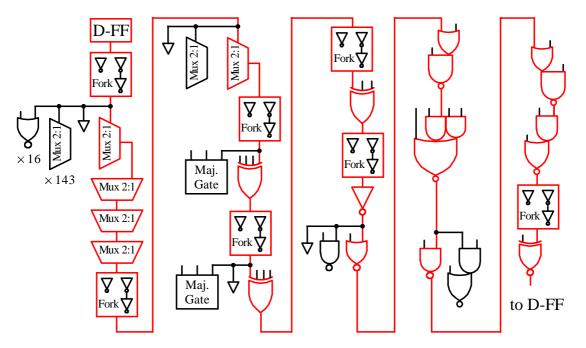

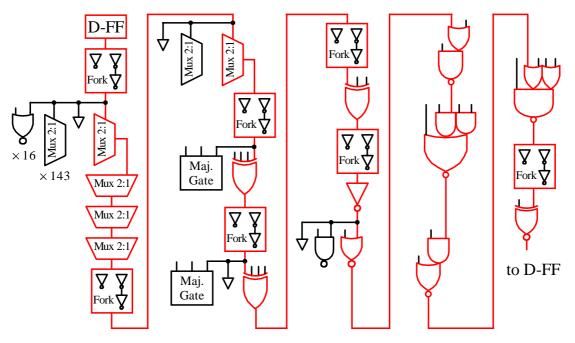

|   | 5.2        | Radix<br>5.2.1<br>5.2.2<br>5.2.3                                              | -4 FP Divider       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       < | 86<br>86<br>86<br>87                             |

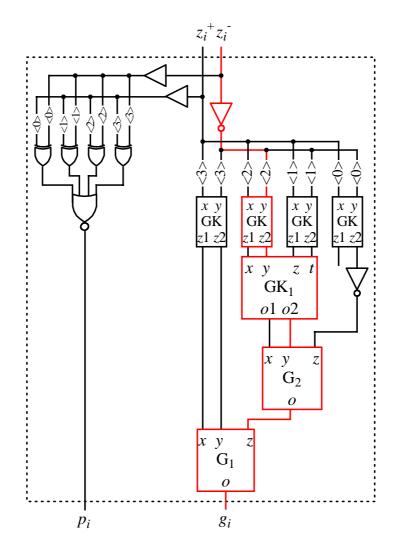

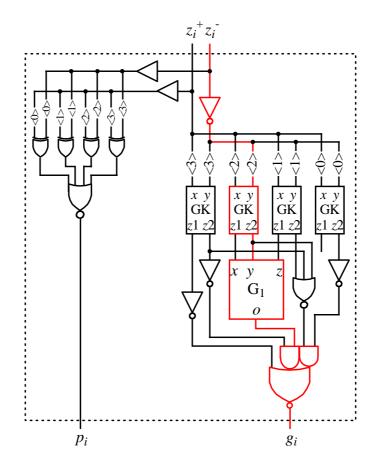

|   | 5.2<br>5.3 | Radix<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                            | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86<br>86<br>87<br>97                             |

|   |            | Radix<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                            | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86<br>86<br>87<br>97<br>102                      |

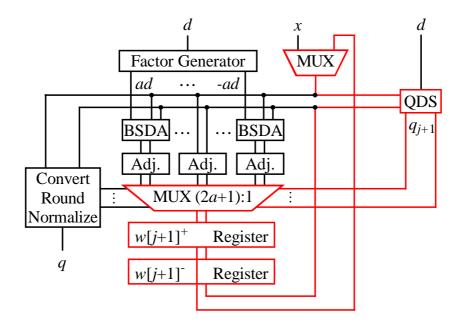

|   |            | Radix<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Radix                   | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86<br>86<br>87<br>97<br>102<br>102               |

|   |            | Radix<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Radix<br>5.3.1          | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86<br>86<br>87<br>97<br>102<br>102               |

|   |            | Radix<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Radix<br>5.3.1<br>5.3.2 | -4 FP Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86<br>86<br>87<br>97<br>102<br>102<br>103<br>105 |

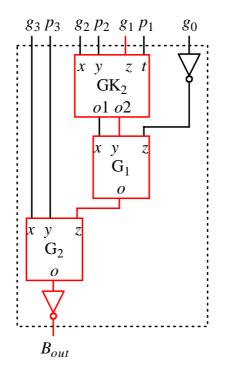

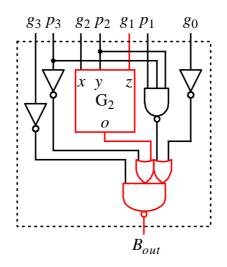

|   |     | 5.3.6   | Convert, Round and Normalise Unit                | 109 |

|---|-----|---------|--------------------------------------------------|-----|

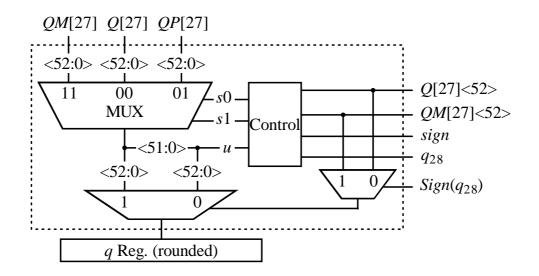

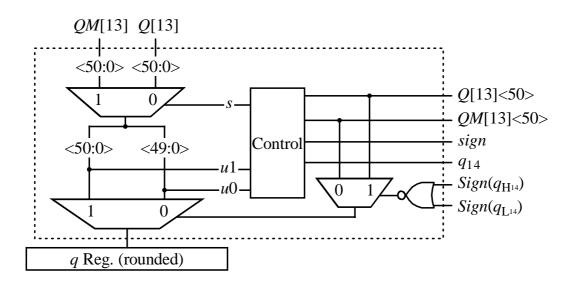

|   | 5.4 | CRN I   | Unit                                             | 109 |

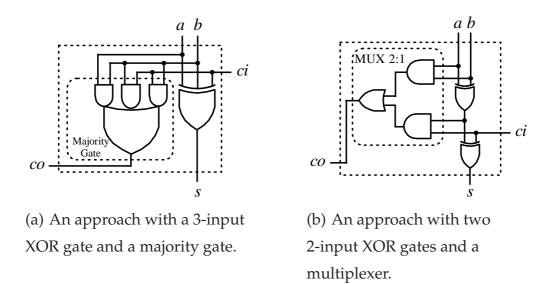

|   |     | 5.4.1   | Previous Approaches                              | 109 |

|   |     | 5.4.2   | New Approach                                     | 112 |

|   |     | 5.4.3   | Evaluation of the Proposed Rounding Algorithm    | 117 |

|   | 5.5 | Summ    | nary                                             | 119 |

| 6 | Dec | imal Si | gned-Digit Arithmetic, A New Approach            | 121 |

|   | 6.1 | Introd  | luction                                          | 122 |

|   | 6.2 | Backg   | round                                            | 123 |

|   | 6.3 | DSDN    | Number Representation                            | 124 |

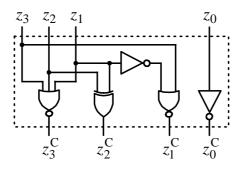

|   | 6.4 | DSDN    | Negation                                         | 125 |

|   | 6.5 | DSD (   | Carry-Free Addition                              | 125 |

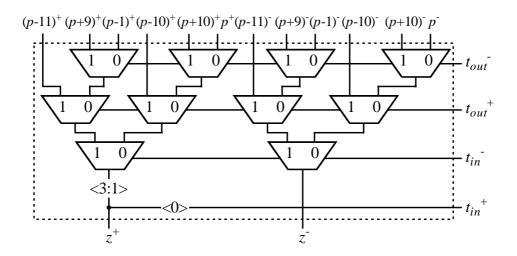

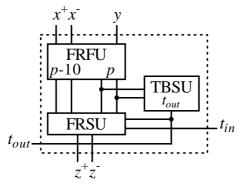

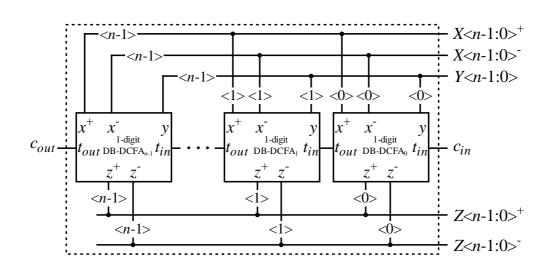

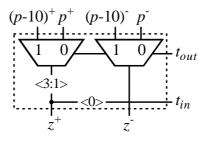

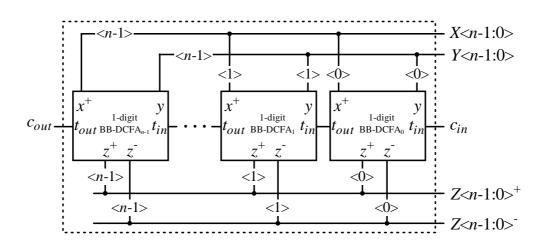

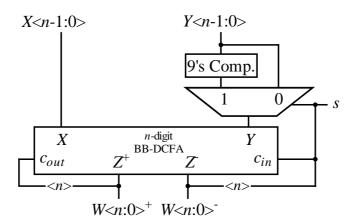

|   |     | 6.5.1   | DCFA with DSD Augend and Addend                  | 125 |

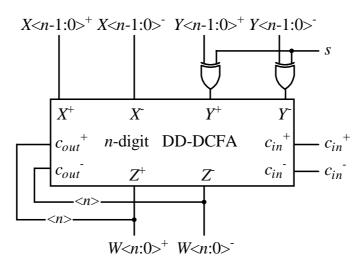

|   |     | 6.5.2   | DCFA with DSD Augend and BCD Addend              | 132 |

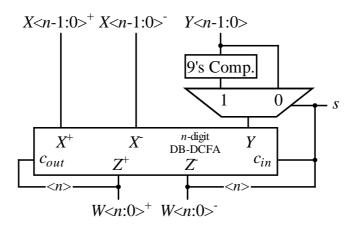

|   |     | 6.5.3   | DCFA with BCD Augend and Addend                  | 136 |

|   | 6.6 | DSD (   | Carry-Free Subtraction                           | 137 |

|   |     | 6.6.1   | DSD Minuend and Subtrahend                       | 137 |

|   |     | 6.6.2   | DSD Minuend and BCD Subtrahend                   | 138 |

|   |     | 6.6.3   | BCD Minuend and Subtrahend                       | 139 |

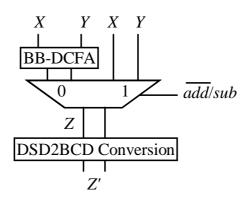

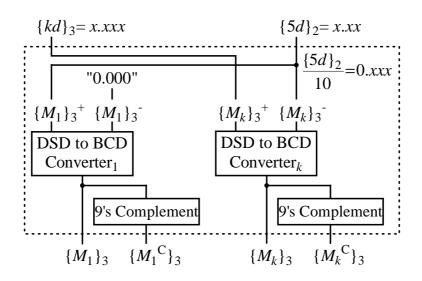

|   | 6.7 | DSD t   | o BCD Conversion                                 | 140 |

|   |     | 6.7.1   | Assumptions and Definitions                      | 140 |

|   |     | 6.7.2   | Algorithm                                        | 141 |

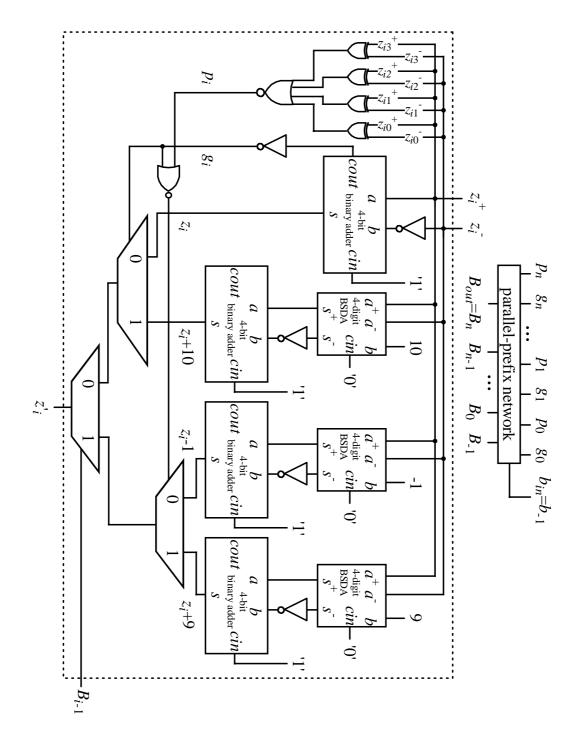

|   |     | 6.7.3   | Implementation                                   | 143 |

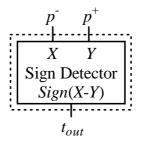

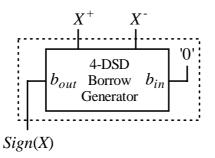

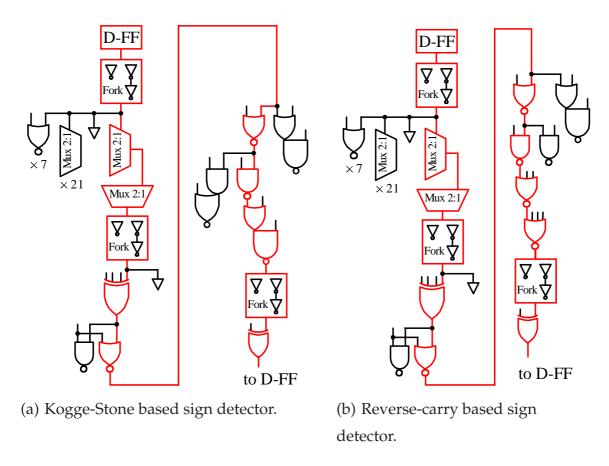

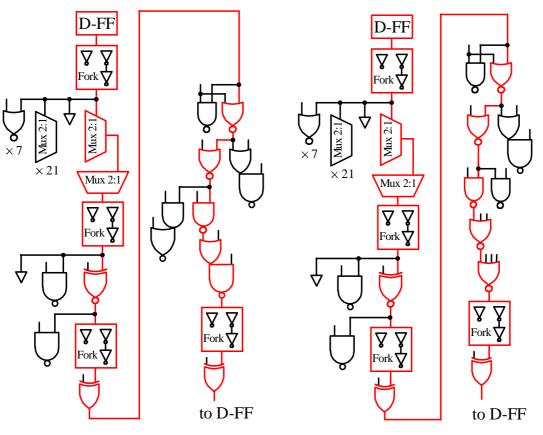

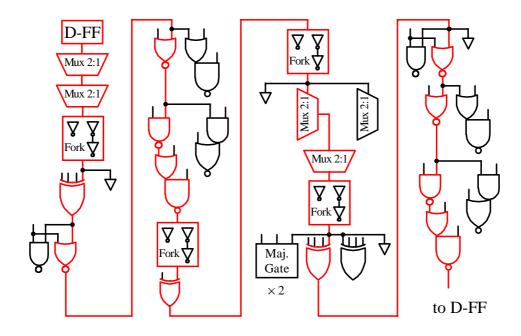

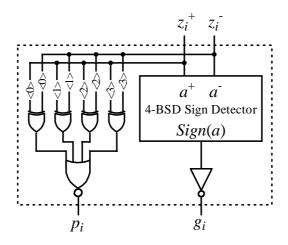

|   |     | 6.7.4   | DSD Sign Detection Using DSD2BCD Algorithm       | 145 |

|   |     | 6.7.5   | Combined BCD Adder/Subtractor                    | 145 |

|   | 6.8 | Evalua  | ation                                            | 145 |

|   | 6.9 | Summ    | nary                                             | 147 |

| 7 | Con | npariso | n Multiples Based Decimal Floating-Point Divider | 149 |

|   | 7.1 | Introd  | luction                                          | 150 |

|   | 7.2 | Digit l | Recurrence Based Decimal Division History        | 150 |

|   | 7.3 | DFP R   | Representation in IEEE 754R Standard             | 151 |

|   | 7.4 | DFP D   | Division Definition                              | 152 |

|   | 7.5                                           | Precis                                                                                                                      | ion and Rounding Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                                                                                 |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|   |                                               | 7.5.1                                                                                                                       | Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                                                                                 |

|   |                                               | 7.5.2                                                                                                                       | Rounding Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                 |

|   | 7.6                                           | DFP I                                                                                                                       | Division Through SRT Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                 |

|   |                                               | 7.6.1                                                                                                                       | Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                                                 |

|   |                                               | 7.6.2                                                                                                                       | DFP Division Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                                                 |

|   |                                               | 7.6.3                                                                                                                       | Convert and Round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8                                                                                 |

|   |                                               | 7.6.4                                                                                                                       | Dealing with Exact Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                 |

|   | 7.7                                           | Imple                                                                                                                       | mentation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $16$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                 |

|   |                                               | 7.7.1                                                                                                                       | DFP versus Previously Proposed Binary Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                 |

|   |                                               | 7.7.2                                                                                                                       | Determining the QDS Function Operands Precisions 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                 |

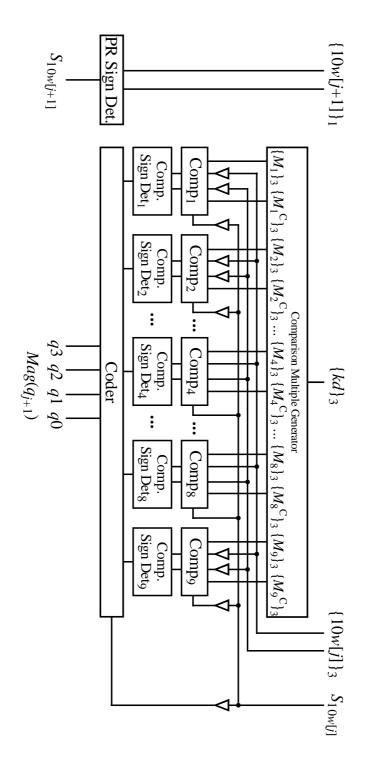

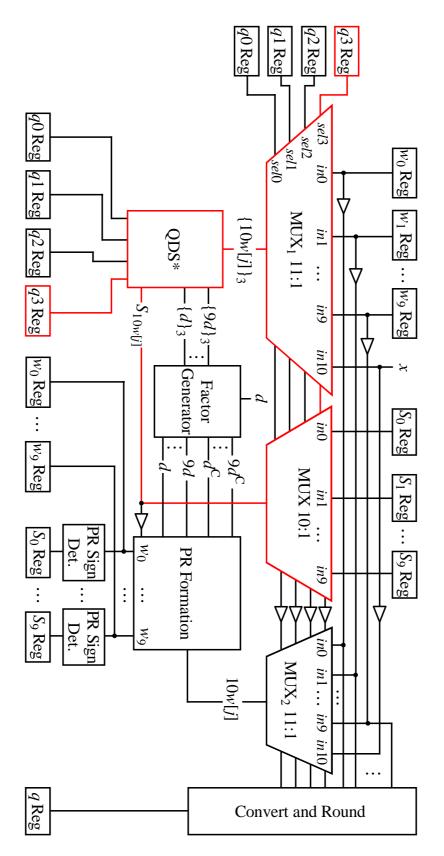

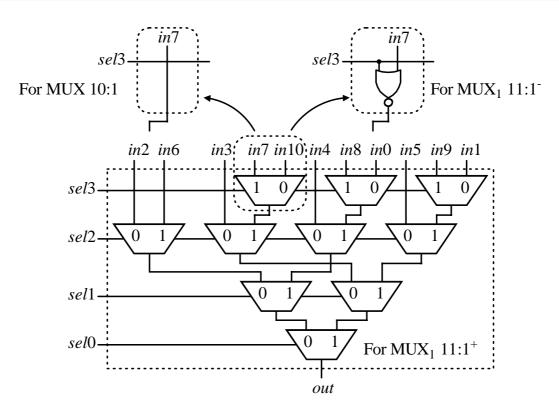

|   |                                               | 7.7.3                                                                                                                       | QDS Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                 |

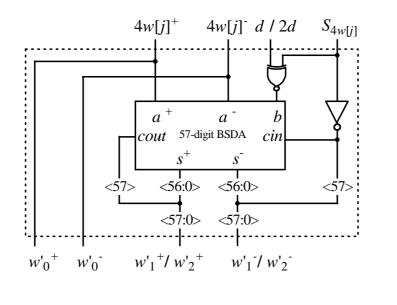

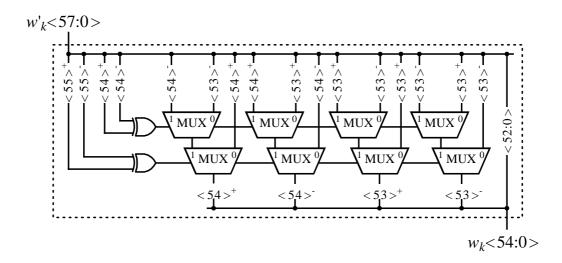

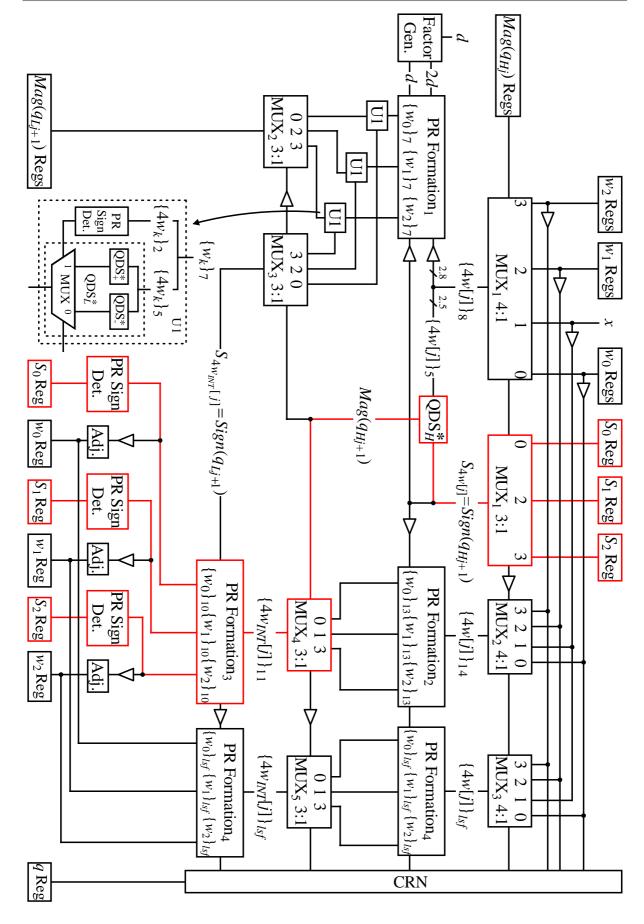

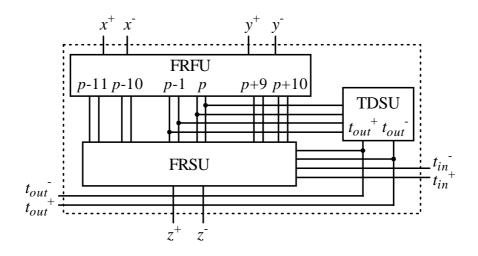

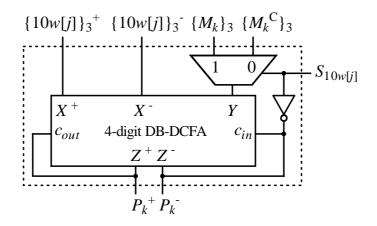

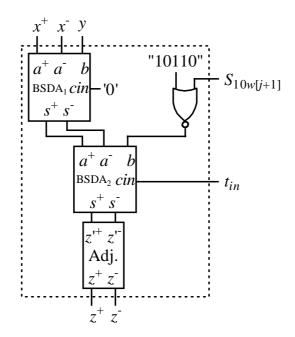

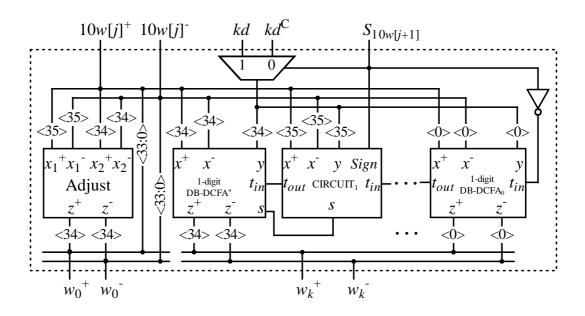

|   |                                               | 7.7.4                                                                                                                       | Recurrence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                 |

|   |                                               | 7.7.5                                                                                                                       | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                                 |

|   | 7.8                                           | Summ                                                                                                                        | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                 |

| 8 | Tim                                           | ing Eva                                                                                                                     | aluation of the Floating-Point Dividers 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                 |

|   | 0.1                                           | ام مسلمی آ                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{c}$                                                                      |

|   | 8.1                                           | Introd                                                                                                                      | luction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $18$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ζ                                                                                 |

|   | 8.1                                           | 8.1.1                                                                                                                       | Iuction    18      Functional Evaluation    18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |

|   | 8.1                                           |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                                 |

|   | 8.1                                           | 8.1.1<br>8.1.2                                                                                                              | Functional Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2<br>3                                                                            |

|   |                                               | 8.1.1<br>8.1.2<br>Logica                                                                                                    | Functional Evaluation18Timing Evaluation1818                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2<br>3<br>5                                                                       |

|   | 8.2                                           | 8.1.1<br>8.1.2<br>Logica                                                                                                    | Functional Evaluation18Timing Evaluation18al Effort1818                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>3<br>5<br>7                                                                  |

|   | 8.2                                           | 8.1.1<br>8.1.2<br>Logica<br>Radix                                                                                           | Functional Evaluation18Timing Evaluation18al Effort18-4 FP Divider Timing Evaluation18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2<br>3<br>5<br>7<br>8                                                             |